走過 路過 不要錯過…十個使用 Cadence® Allegro® 17.2-2016 的最佳理由將幫助您進一步了解新版功能如何優化 PCB 設計流程,讓您在面對 IoT、智慧穿戴設備等新設計挑戰,更加得心應手!

理由一:支援進階的軟板及軟硬結合板設計-縮短您的設計時程

因應愈來愈多電子設備及產品紛紛導入軟板或軟硬結合板的設計,Allegro 17.2-2016 增加一些針對軟板及軟硬結合板設計方面的新功能,幫助 PCB 設計者縮短與機構端資料反覆傳輸疊代確認問題的次數及時間,進而減少整體預算的花費。

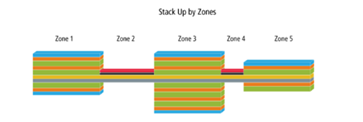

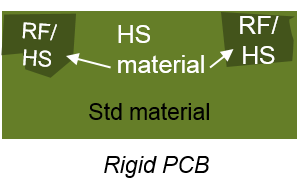

軟硬板可藉由 Zone 功能更快速簡單地做區域劃分疊構特性,並改善 MCAD-ECAD 雙方協同設計的成效;新功能也能使板材鑲嵌一部份的 RF/High-Speed 電路材料,以節省達 25% 的使用空間。

此版本針對軟板及軟硬結合板設計提供多達 12 種的新板材及 19 種的表面處理方式,使用者也能自訂相關的板材及表面處理,並使用新的層與層間的檢查機制來進行幾何關係的檢查。

理由二:全新即時協同設計功能-與您的團隊成員同步設計,縮短 80% 複雜的佈線時間

您是否經歷過很緊湊的設計時程?是否希望能與團隊成員在同一 PCB 設計專案上同步進行設計工作?

現在隨著 Allegro 17.2-2016 的發佈,團隊成員能夠連接到 Allegro PCB 的共用資料庫,在同一份設計專案上輕鬆地一起同步進行設計工作,若有成員進行任何編輯時,其他成員都能立即看到變化。全新 Allegro 即時協同設計功能,將可以縮短 80% 複雜且密集的佈線設計時間。

理由三:新的 Padstack 編輯器-更加簡單易用並支援更多樣的焊盤結構

透過圖形化介面及引導式的設定步驟建立 Padstack,將大幅提高您的工作效率。新版編輯器能輕鬆地定義Padstack 所需的屬性,並且提供許多新的幾何形狀,使之容易地建立複雜的 Padstack, 使用者也可以建立幾個新的基本形狀如甜甜圈形狀、圓角矩形或倒角矩形…等,這些 Padstack 不僅易於建立,也有助於簡化一部分的設計流程。17.2 的編輯器還提供了 Route Keepout 設定選項,使用者能依設計需求定義各層隔離時的形狀及禁制區大小。

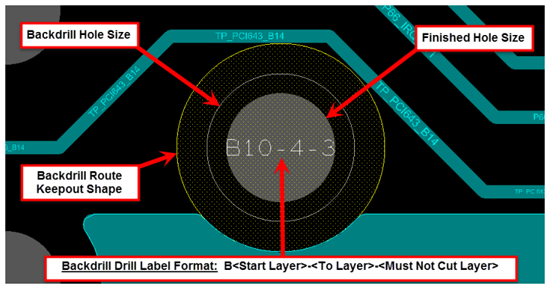

理由四:業界最好的 Backdrill 功能再進化-清晰易懂的 Via 標籤顯示多元 Backdrill 資訊

Allegro PCB Designer 是業界第一個提供 Backdrill 功能的軟體; Cadence 採納客戶建議,在 Via 的設計規範與標籤的顯示上增加多元的 Backdrill 資訊,幫助使用者在設計過程更加有效率,並能預先避免錯誤發生。

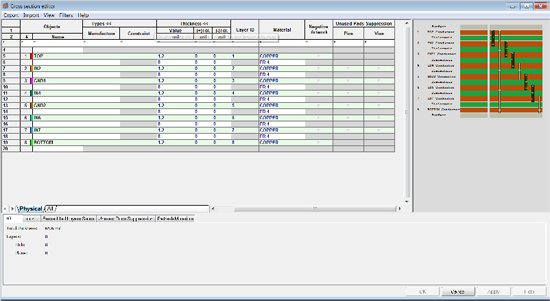

理由五:新的 Cross Section 編輯器 – 簡化設計的設定及相關物件疊構的規範

Cross Section 編輯器讓我們能夠定義如疊構設定、Dynamic unused pad suppression 及 Embedded component 設定。疊構設計以圖像方式呈現,可顯示與定義鑽孔方向,可增加 Layer pair 或使用者自訂的層面。其他增強部分包括了材料字元長度可從 19 到 250 個字元,各層厚度也加入正/負公差設定,Via 標籤的名稱可自訂,並且能控制或預防層面被編輯等功能。

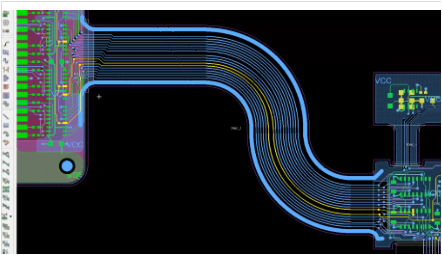

理由六:先進的輪廓弧度感知佈線能力–有效節省軟板設計時間

無論您在進行軟板、軟硬結合板或硬板設計,Allegro PCB 皆已增強弧度感知佈線能力。Enhanced Contour 功能在使用者執行 Add Connect 時,面對已存在的走線或 Route keepin,都能沿著其輪廓快速帶出走線,更能有效節省設計時間。使用者現在只需要在作圖區點選走線的起始與結束兩端點後,就能輕輕鬆鬆依照對應的輪廓實現走線。

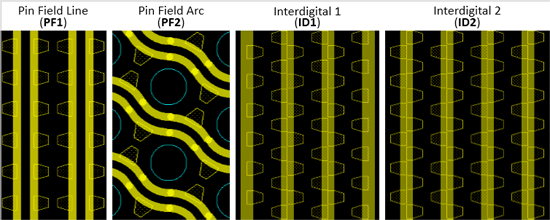

理由七:Tabbed Routing – 特別在 BGA Breakout 的區域內,管控關鍵信號的阻抗與串擾

當 BGA IC 有非常多的 Pin 及很小的 Pin pitch 時, IC 內部走線的寬度相對地也會比平常走線來得窄,這代表單一信號和差動信號都需通過這些區域。而更糟的是,Pin 的區域中充滿了很多 Void,使得阻抗變得難以控制。現在藉由使用 Allegro 17.2-2016,您將能透過新的方法管控這些區域的信號阻抗,讓您在平行走線間加上梯形Shape 來補償阻抗並運用相關的檢查機制,以因應設計規範要求,如:Tab 的數量及其間距。

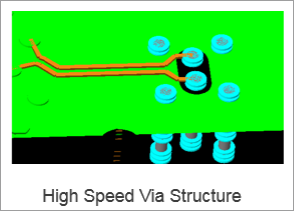

理由八:Allegro Sigrity 最佳整合 – 使用 Sigrity 驗證 Allegro 的 Return path via 結構

先前已向各位介紹過 Allegro 16.6-2015 增加 6 種新的 Via structure,而現在新版Allegro 17.2-2016 更能在您的設計裡,添加已經由 Sigrity 驗證過的 Via structure,來節省 PCB Layout 設計的時間,並避免在佈線後期驗證過程中發生任何的意外。

理由九:新的設計規範檢查 (DRC)

Cadence 持續增進 Allegro PCB Editor 的設計規範功能,除了新的 Backdrill 規則及軟板和軟硬結合板的 Inter-layer 檢查條件之外,還新增 Drill DRC 及四種型態的銳角偵測檢查。Drill DRC 現在能透過勾選新的檢查選項之後,讓您的 PCB 設計中所有包含 Pad Ring 的 Pin 或 Via,再以鑽孔的角度來跟其他物件進行間距的檢查。而新增的四種銳角檢查條件包含 Shape 邊緣與 Shape 邊緣夾角檢查、Line 與 Pad 夾角檢查、Line 與 Shape 夾角檢查及 Line 與 Line 夾角檢查,以期後續 PCB 生產能更順利完善。

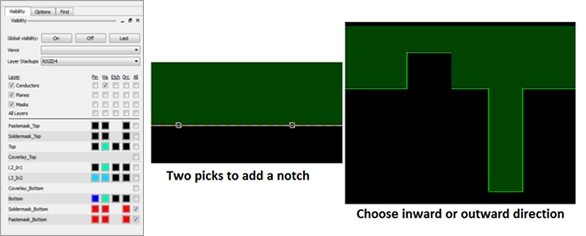

理由十:更加便利的 Allegro PCB Editor

讓 Allegro PCB Editor 更易於使用是 Cadence 一直持續努力的目標,新版 Allegro 17.2-2016 功能提升目的之一就是要減少 PCB 設計所花費的時間,減少您點擊滑鼠按鍵的次數。現在您能依照使用習慣自定義工具列的功能按鈕,並運用 Visibility 面板更便捷地控制層面顯示內容。