高效率的专业仿真中控平台

Virtuoso® Analog Design Environment(ADE) 是建构在 Virtuoso设计平台中最佳的仿真与混合信号设计仿真解决方案,广泛应用在 full-custom、analog、RF IC 设计领域,采用目前业界的仿真与分析标准,在使用上,ADE 提供图形接口、集成波形分析与观测、统计分析仿真结果,以目标导向指定参数范围做仿真分析,并且支持多种仿真器演算 (包含其他非 Cadence 仿真器) 。ADE 在 Virtuoso 环境中使用,无须担心数据转换的问题,更可针对电路中设定的参数依规格范围扫描快速仿真测试,提升您的工作效率。

特点

容易学习,快速上手 |

|

图形接口管理,更有系统 |

|

仿真状态储存,提高工作效率 |

|

集成各种仿真器,更具弹性 |

|

(Virtuoso Spectre Simulation / Virtuoso APS / Virtuoso AMS Designer / Virtuoso UltraSim / Virtuoso XPS) |

|

提高仿真广度与除错精准度,仿真更专业 |

|

可视化图像菜单,加快电路除错 |

|

强大的寄生仿真分析能力,提高成功率 |

|

PDK 应用,加速设计流程 |

流 程 特 点

PDK 应用大幅加快设计流程而提高工作效率

集成 Virtuoso Multi-Mode Simulation 实现仿真、射频、混合信号仿真验证

强大的寄生仿真分析能力,大幅提高第一次就设计成功的机率 ( first-pass success )

清楚而简单的操控接口,协助用户快速的找到电路问题

EASY-TO-USE INTERACTIVE SIMULATION ENVIRONMENT

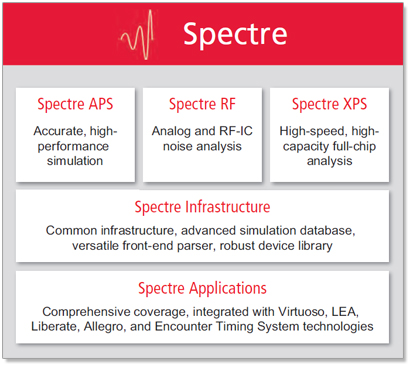

ADE 提供完整功能让所有电路设计者快速完成仿真设定、环境建构与分析仿真结果,环境中集成了 Virtuoso Spectre Simulation、Virtuoso APS、Virtuoso AMS Designer、Virtuoso UltraSim、Virtuoso XPS。

用户在设计流程中可快速且轻易地通过可视化的图形接口了解仿真或混合信号中特定参数对电路产生的效应,内建的 OCEAN 程序语言更加速 bash 演算,而通过 OASIS (Open Artwork System Interchange Standard) 集成套件,ADE 可轻松的与自家 Virtuoso 或业界使用的其他仿真器集成使用,加速电路设计。

BUILT-IN WAVEFORM DISPLAY AND SIGNAL ANALYSIS CAPABILITIES

新一代波型显示器 (ViVA),包含波形计算功能,针对各种设计结果数据如电压、电流、仿真参数、工作点做代数方程式运算,并提供更完善的 post-simulation 分析环境,在仿真与混合信号分析上支持更进阶的波形分析模式,如 noise、corner、statistical、RF plots…等,支援 PNG、BMP、JPG、PPM、TIF、PDF、SVG 文件格式。

INTERACTIVE SIMULATION

让用户可以快速改变参数值,减少电路设计者仿真流程所花的时间。

VIRTUOSO AMS DESIGNER SIMULATOR

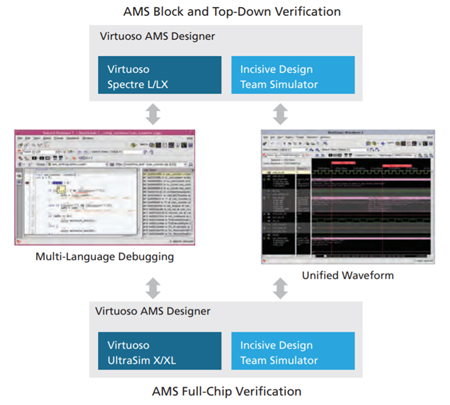

Cadence Virtuoso AMS Designer 集成 Cadence Virtuoso 类比仿真器与 Incisive 数字功能验证于同一仿真与验证平台中,使得仿真、无线射频、内存及芯片系统等…混合信号设计在全客制化的环境实现。

Cadence Virtuoso AMS Designer 支持 Verilog-AMS 及 VHDL-AMS 混合信号语言,当类比与数字连接时用户可选取不同的类比仿真器于不同的设计仿真阶段,例:block-level 的仿真与无线射频设计 (RF design) 时考虑精确度可使用 Spectre Simulation,或欲同时考虑到仿真速度效能则可选择 APS (Accelerated Parallel Simulator),而当考虑 Full-Chip 功能验证时可挑选 UltraSim 并搭配数字 Incisive 弹性与便利执行此仿真、验证的设计流程。

特点

提供 Virtuoso 类比及 Incisive 数字仿真 |

|

支持 Virtuoso ADE (Analog Design Environment) 中类比设计流程所使用的仿真参数模型,亦可使用于数字 Incisive 验证环境中 |

|

支持由上而下 (Top-down) 的设计方法,使在初步设计时间的错误能够提早被察觉,以确保设计可准时进入投片流程 |

|

支持混合信号的硬件描述语言 (Verilog-AMS 及 VHDL-AMS) 使仿真更加快速 |

|

结合 RF 封包分析与数字基频 (digital baseband) 仿真,加快 AMS 对 RF 电路仿真速度,尤其是针对 SPICE 级的精确度仿真速度更明显提升 |

|

提供可选式的类比仿真器,让用户满足仿真速度与效能考虑 |

|

支持图形用户界面 (GUI) & 可通过 batch mode 下指令 (command) 来增加仿真的便利性 |

|

支持以数字区块为主的混合信号验证 & 导入低功率混合信号验证解决方案 |

Virtuoso AMS Designer 验证流程,可满足电路设计在混合信号验证分析上整个流程的需要

支持多种硬件语言及「MEET-IN-THE-MIDDLE」的设计方式

Cadence Virtuoso AMS Designer 支持来自不同来源的芯片系统设计 IP 格式,包含 Verilog-AMS、VHDL-AMS、Verilog-A、Verilog、VHDL 及 SystemC 硬件语言。当于 Virtuoso Schematic Editor 使用 HDE 架构设计复杂的混合信号项目 (包含上述硬件语言及 spice、Spectre Simulation) 时,AMS Designer 会自动插入接口组件 (IE / interface elements) 做类比与数字间的信号转换,并且它可将 bottom-up 的精确性与 top-down 的快速性作设计流程集成(MEET-IN-THE-MIDDLE),它实现了速度需求和芯片精确性之间的最佳平衡性,而且以最佳的考虑来执行仿真。

兼顾类比与数字仿真需求的混合信号仿真器

集成式的仿真引擎,不仅提高混合性信号芯片仿真之完整性,更让使用者在仿真的准确性及效率间不再左右为难。因为依用户的需求来选择仿真器,所以用户可在仿真、验证设计流程中更具弹性且能满足仿真速度与效能考虑,让使用者的创意永远 Time To Market。

它的演算技术是建构在 Virtuoso Spectre Simulation、APS、UltraSim 这些类比仿真器,并且能兼容与 INCISIVE 数字仿真器所构成的集成混合性信号仿真器。

类比信号为主或数字信号为主的流程

针对混合信号电路设计,Virtuoso AMS Designer 使用 ADE 的 netlisting 方式将电路符号方块、行为模型方块…等不同型式方块独立处理,而 Virtuoso AMS Designer 数字验证使用 Incisive,Incisive 环境提供测试分析、Specman 及验证平台。

针对数字设计为主的电路,AMS Designer 会以本身的 Incisive 环境来完成数字验证工作,此时类比与数字间信号传递转换可使用一信号控制文件 (single control file) 做为定义,类比方块则被集成到数字的 SoC 中,如此类比与 RTL 设计方块间可便利的调整其仿真精确度与速度以取得可接受平衡点。而交互式的仿真接口将开启 SimVision 并提供从电路图 cross probe 的功能。

针对类比设计为主的电路,执行 AMS 电路仿真前 netlist 必须先经过编译 (compile) 与合成 (elaboration) 动作,若使用 ADE 中 ”Netlist and Run” 单键功能,便会自动依照以下顺序完成 AMS 仿真程序:

线路图转换为 Verilog-AMS Netlist |

|

编译 Netlists |

|

执行合成 |

|

执行仿真 |

以上每个工具产生各自的纪录档案,若仿真失败会在 CIW (command Interpreter window) 信息中显示信息,参考各记录档案可明确了解须修正的错误。

AMS Designer 可依使用者习惯区分不同的方式来做验证

AMS-ADE 支持容易上手的 Virtuoso 图形用户界面 (GUI) 的集成验证方式来加速验证过程所需的时间,而针对数字 IC 设计者常习惯在 batch mode 去下指令 (Command),AMS-irun 也支持 Incisive 仿真器通过命令行的方式去执行指令来做验证。

「支持以数字区块为主的混合信号验证」与「导入低功率混合信号验证解决方案」

针对数字区块为主的设计,采用事件驱动 (Event Driven) 的架构以及 wreal 的模型化来达到高性能,而且 AMS 支持指针驱动 (Metric Driven) 的验证方式可通过涵盖率 (coverage) 这项指针来提升生产力及完整性,另外,针对仿真混合性信号设计也导入低功率解决方案来协助设计者设计验证低功率的电路设计。