電子設計自動化領域領先的供應商 Cadence,與諸位分享 Cadence Allegro、Sigrity 等產品最新的科技成果和進展,並向電子設計工程師展示 Cadence 獨有的 PCB 和封裝設計解決方案。「升級到 Allegro 17.2-2016 的 10 大理由」系列繼續推出,歡迎共同探討~~今天帶來的是「升級到 Allegro 17.2-2016 的 10大理由之 9:新設計規則檢查」。

Allegro PCB 17.2-2016 發行版本增強了鑽孔相關功能

我們為實際的鑽孔工具、背鑽工具、方形孔、沉頭孔等增加了焊點定義,並增加了鑽孔容差。應廣大用戶需求,背鑽位置現在完全支援DRC 間距規則。(見升級到Allegro17.2-2016 的10 大理由之 4:行業領先的背鑽能力)。

同時更新的還有標準鑽孔間距 DRC 的行為變化。追溯到 16.2 版本,我們提供了鑽孔 DRC 來支持「內層無盤工藝」功能。該檢查功能只有在焊點被刪除、或者焊點尺寸比鑽孔小時(測位焊點)才有效。從那以後,出現了針對鑽孔檢查的大量需求,無論焊點是否存在。

增強的鑽孔 DRC

在 Allegro PCB 17.2 中,分析模式中添加了新的間距選項控制開關—稱為「Checkholes within pads」的設計模式功能表。

打開開關,運行鑽孔檢查時直接使用鑽孔資訊(在該 DRC 計算模式下,與是否存在跟鑽孔相連的焊點無關)。換句話說,無論是否存在焊點,都會進行鑽孔檢查。 |

|

關閉開關,鑽孔檢查只有當焊點被抑制或處於未定義狀態、暴露空孔時才相關。這是預設的設置,並與之前版本相容。 |

銳角檢測

設計規則 DRC 也引入了基於四個角度的檢查。銳角檢查通過 new Setup-> Constraints -> Modes command 運行,然後選擇 Design Modes (Acute Angle Detection) 進入到 Analysis Modes。DRC 模式可設置為 On-line、Off 或 Batch 模式,角度可在 < 0 : 90 > 度範圍內進行設置。

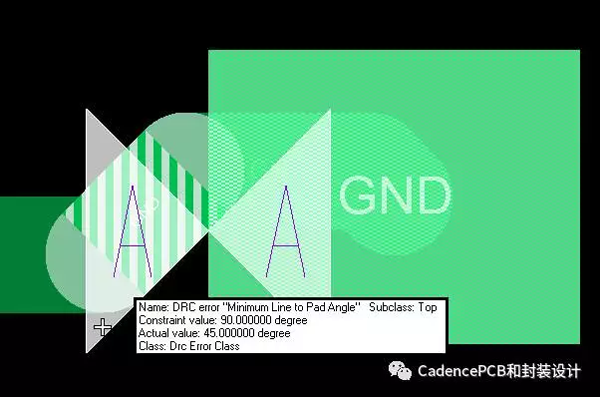

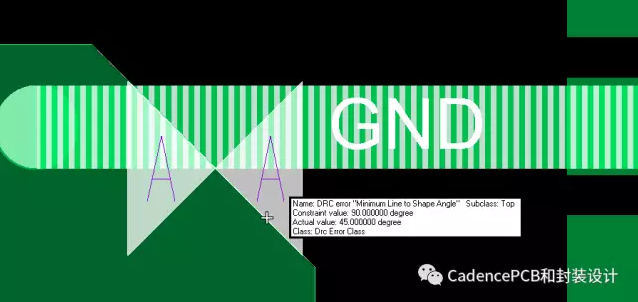

在 Acute Angle DRC 視圖,DRC 標記包括字元「AA」,則為報錯。Acute Angle DRC Checks 表現為:

最小 shape 邊緣到邊緣 - 銅層輪廓為銳角且角度過小

最小線到焊點 - 焊點入口與線段產生銳角

最小線到角度 - 銅層與線段交叉產生銳角

最小線對角度 - 線段交叉產生銳角

Net Class-Class 規則分配

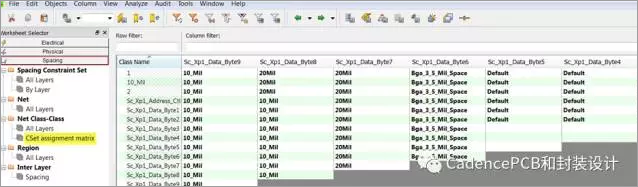

很多用戶擔心我們在約束管理器中展示 Net Class-Class 規則的方法。我們收到的回饋是執行過程冗長、難以理解。我很高興地宣佈我們的約束管理器團隊開發了一個選項,可以看到二維陣列的規則分配。打開 Spacing Domain – Net Class-Class 工作表,即可看到新的「Cset assignment matrix」。

延伸閱讀

文章授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」