電子設計自動化領域領先的供應商 Cadence,與諸位分享 Cadence Allegro、Sigrity 等產品最新的科技成果和進展,並向電子設計工程師展示 Cadence 獨有的 PCB 和封裝設計解決方案。「升級到 Allegro17.2-2016 的 10 大理由」系列繼續推出,歡迎共同探討~~今天帶來的是「升級到 Allegro 17.2-2016 的 10 大理由之 4:行業領先的背鑽能力」。

背鑽的發展歷程

15 年來,在很多電子設計中處理 5Gbps 或更高頻率的高速介面佈線已越來越常見。在信號貫孔上存在 Stub 的情況下,高速信號換層將會對信號完整性產生巨大影響。總的來說,這些短截線會造成阻抗不連續和信號反射,嚴重影響有效資料傳輸速率的提升。

如何消除電子短截線?

使用一種稱之為背鑽的制板工藝,有時也被稱為控制深度貫孔。 |

|

做好規化和控制,保證高速信號走在特定的佈線層,以此來減小 Stub 的影響。 |

|

用盲埋孔和微孔技術來布高速信號,這種方案可以解決一些局限和擔憂,但會增加製造成本,而且壓接連接器的管腳仍需用背鑽技術來消除 Stub。 |

早些年,製造商會根據關鍵網路清單,識別使用背鑽的地方並做適當的調整。

在設計中引入背鑽過程,有時對管理來說是個噩夢,需要與製造商更緊密合作。製造商會移除盡可能多的指定高速信號的短截線,根據增加的背鑽尺寸調整每個背鑽位置的特性、驗證銅間距,來維持設計完整性。

為了讓設計資料傳遞更順暢,在 Allegro 15.7 中,早已為簡化製造端的資料處理打下了穩固的基石。

作為曾經的客戶,2005 年底,我曾是 Allegro® PCB Designer 15.7 Beta 測試團隊的一員。我很高興見證 / 測試了 Allegro 新的背鑽解決方案。通過允許設計人員標識需背鑽的網路,基於器件和引腳的屬性分析並識別背鑽位置等功能,使 Allegro 更上一層樓。需背鑽的位置包含在背鑽報告中,標有特殊的背鑽符號,生成用於生產的 NCDrill 檔。即使有了這些提升,但仍然存在人為確保一致性的步驟(支援背鑽位置有多種焊盤,手動設置背鑽禁止區,允許製造商調整背鑽尺寸)。

隨著時間的推移,可以清楚地認識到未來的增強將會改進這個流程,會提供分析設計並且調整背鑽位置特性的功能,同時生成完整的製造資料包來實現流水化製造。

Cadence 與製造商和客戶合作,調整了現有的解決方案,除了製造商移除大部分後處理步驟,還增強了幾個區域的工具來支援背鑽流程。作為一位元產品工程師,我能夠根據我自己之前作為客戶的經歷、並搜集客戶們的回饋來調整這些功能。

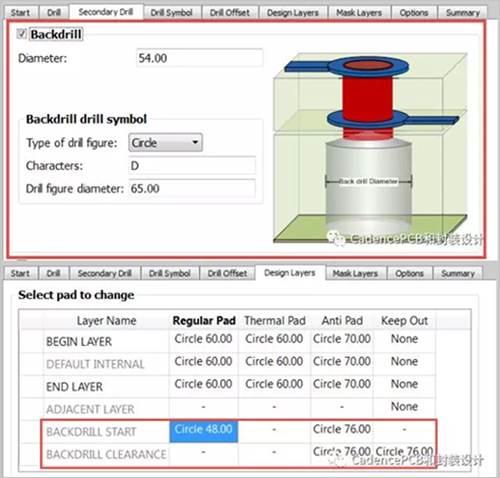

封裝庫中的焊盤支持背鑽定義 |

|

有特定標識的背鑽尺寸 |

|

增強背鑽焊盤進入和焊接掩膜 |

|

增加層禁區 / 間距 |

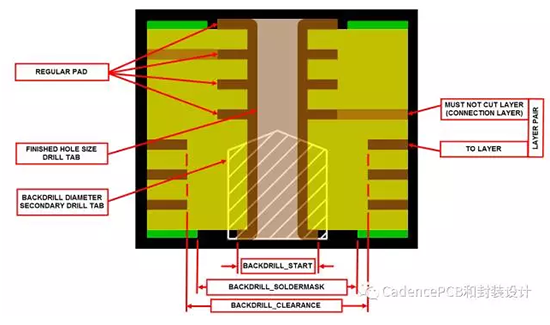

典型的背鑽位置

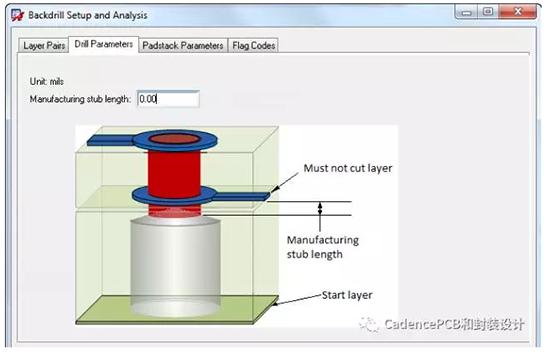

製造 Stub 長度-背鑽後保留 Stub 長度(進階設定) |

|

從不可切割層向下測量的剩餘製造短截線長度,其表示電介質目標背鑽深度 |

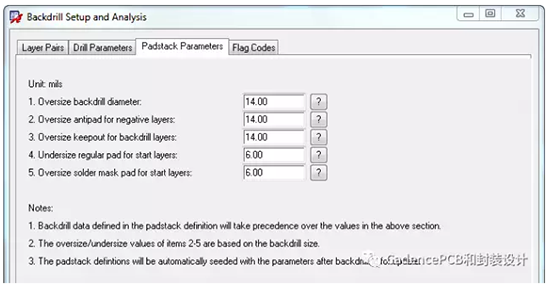

基於參數的設計層焊盤更新建成了背鑽分析 |

基於設計分析的改進模型可以快速定義 / 檢查背鑽層對規則 |

|

初始化:從頂層及底層的最深的背鑽層 |

|

分析:最小化的電子短截線長度或最小化層對 |

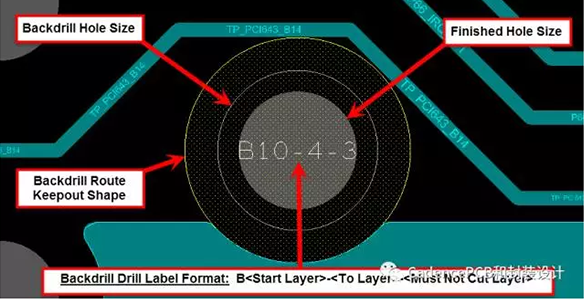

帶有特殊鑽孔標識的背鑽直徑,用來說明背鑽方向和深度 |

|

基於焊盤定義的間距自動生成走線禁布區 |

|

在背鑽位置不再需要創建特殊的焊盤或禁止區 |

Show element 指令可以報告在背鑽位置引腳 / 貫孔的背鑽資料 |

|

基於在焊盤定義的背鑽資料,現在在鑽孔圖例和製造 NCDrill 檔中報告真實的背鑽尺寸 |

|

不再需要製造商基於電鍍通孔調整尺寸 |

|

Backdrill Legends 現在報告不能切割層、深度和製造短截線資訊 |

|

畫出跨區域細節,現在報告背鑽跨度 |

|

在背鑽過程中識別全部的測試點 |

|

在背鑽位置沒有測試點或增加測試點之外的鑽孔 |

提升後的背鑽解決方案解決了所有的疑惑點,消除了由於引入背鑽所帶來的擔心。不再增加製造商的一次性工程費用(NRE),不再增加關於引入不同貫孔和疊加技術的成本。可以傳遞給製造商一個更完整的製造資料包,其中包含 IPC-D-356 和 IPC-2581 中的背鑽資料資訊,以及用於傳達背鑽意圖的完整文檔。

延伸閱讀

文章授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」