快速完成复杂封装设计

随着市场对产品功能「集积化」的需求,高 pin 数 / 多功能的高级零件封装设计也更显重要,为了有效地设计这些复杂的封装,需要一个复杂的设计工具来解决电气和物理方面的限制。Cadence® 封装设计技术以其高效、灵活和可靠的技术来完成密集先进的封装而享誉全球。若再另外搭配集成的信号和电源完整性分析选项可确保在整个设计周期中共同解决电气和物理难题。使用 Cadence 封装设计技术,设计人员有可能在最短的时间完成项目甚至可以首次通过符合规格以满足压缩时间表的要求。

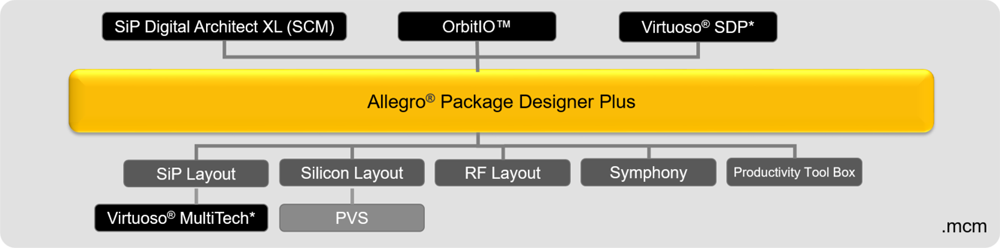

Cadence 封装设计解决方案

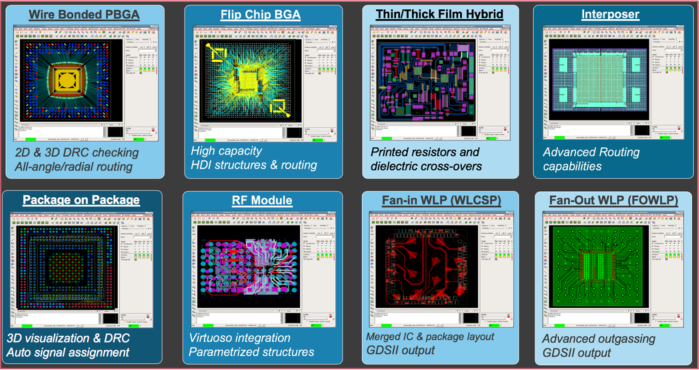

现在,Package 封装设计已成为 IC-Package-Board 设计流程中的关键环节。 Cadence Allegro® 平台为 PCB 和复杂封装的设计和实现提供了完整且可扩展的技术。不论您是 Lead Frame、WireBond、flip-chip 或 Interposer 等等的封装技术,您都可以利用 Allegro X Advanced Package Designer 专为封装设计所开发的各项方便易用的功能优化复杂的单芯片和多芯片的 Wirebond 和 Flip Chip 设计,来达到快速集成产品特性和功能优化之目的,以降低成本和性能,同时又能缩短项目时间。

Constraint-Driven 的业界标准和技术可实现高级 OSAT 和晶圆厂从单芯片到复杂的系统规划和封装设计。

Cadence 封装设计解决方案可实现高效的封装设计技术,具有规范意识的基板布线设计。若另外需要布线模型萃取、模型建立和信号 SI/PI 分析等功能有以下产品:

Allegro X Advanced Package Designer |

|

SiP Layout Option 选购 ⇒ 升级到标准 SiP 版 |

|

Silicon Layout Option 选购 ⇒ Wafer Level Package 专用 |

|

RF Layout Option 选购 ⇒ 绘制 RF 零件 / Layout |

|

Symphony™ Team Design Option 选购 ⇒ 多人 (实时) 同步设计 |

|

System Connectivity Manager 另购 ⇒ 表格式的线路图工具 |

|

OrbitIO™ interconnect designer 另购 ⇒ 可做 IC / PKG / PCB 的最佳接点优化规划 |

效益

技术文件套用架构~可简化并自动化设计设置 |

|

从前到后有线路图和无线路图的流程,为逻辑管理提供了业界最灵活的模型 |

|

动态式组件库建立可简化数据输入 |

|

wire-bond、flip-chip、stacked 和 embedded die 等智能定义可确保布局时有按正确的构造进行 |

|

先进的 Bond-shell 生成技术甚至可以使最复杂的多芯片或堆栈式的 Wirebond 设计自动化 |

|

放射状、任意角度的推挤式布线解决了 BGA / LGA 基板布局的独特挑战 |

|

专用于 BGA / LGA 的 DRC / DFM / DFA 检查,可确保在第一时间就能有正确设计以符合生产 |

|

3D 检视和 DRC 比传统 2D 检查更能准确地验证设计 |

|

与 Cadence Innovus 和 Virtuoso IC 设计工具的集成流程,可简化 IC 和封装之间的协同设计 |

|

可搭配 Symphony Team Design 的选项,让多人可同时编辑封装设计以缩短总体设计的时间 |

|

可选购 Silicon Layout Option 来扩展功能,以处理 IC 等级的布局检查和 Mask 验证 |

|

全球超过 400 多个客户使用 |

功能特点

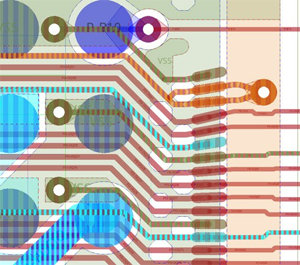

Constraint-Driven 的封装设计架构

Allegro X Advanced Package Designer 包含当今先进封装设计所需的所有功能。其完整的实时 DRC 设计规则检查支持能对应到层压、陶瓷和硅基基板,或如多个 cavities、复杂铺铜及 Wirebond 等多种结构集成的先进封装集成需求。

其易于使用的 Flow Manager 引导您完成每个任务,自动执行创建 IC 封装的基本组成部分的过程,便捷的向导程序可自动快速地建立出封装设计中的各项特定零件或需求,如 WireBond、Power/Ground Rings 和 plating bars 等,更可用 die 和 BGA Wizards 载入的文本文件 (D.I.E.、Excel、AIF2) 以自定字段的方式,自动建立其接点不一的零件。现在您甚至可以由 GDSII 或 DXF 的图形辨识来自动建立所需的零件。

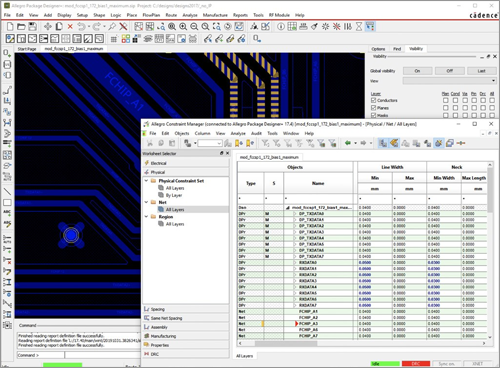

完备的基板建模和规则检查

可藉由完备的物理和电气规则 (constraints) 对设计做最准确的验证和查核,加载由使用者定义的 Technology File,可做为 Physical 实体设计的规范以确保其可制造性,而 Electrical 电气规范可定义重要信号,如延迟和失真的规格,可随时跟 constraints 比对以确保设计能符合制造和电气的种种要求,表格化的 Constraint Manager 可清楚的管控所有的规范。另外,实时的 drc 检查可配合现今复杂且特殊的各种载板设计需求。

可重复套用先前设计结构

Substrate 的迭构和 constraint 信息被记录在 technology 中,当局部设计还是整个设计结构相似时,我们可以套用在设计上不需重新定义以缩短将来设计的时程,制造商或供货商也可以提供包含关键设计规则的 technology file 以帮助推动正确的设计方法来确保辅助供货商的可制造性。

WIREBOND 和 FLIP-CHIP 及 Copper Pillar 的接出样式

Allegro X Advanced Package Designer 提供快速、强大且灵活的 Wirebond 建立和编辑功能,只需要简单几个按键就可建立出 die flags 和 Power/Ground Rings 及各式各样的 bondfinger。Die flags 可以用向导接口自动建立,或是以加载的 TXT/dxf 来建立,而强大的 Power Rings 可建立、切割及合并电源圈以配合现今多重电源的需求。另外也有推挤及群组等功能,在数分钟之内即可建立出所要的打线架构,而真实的 wire profile 可实现 DFM-driven 的设计架构,防范于未然,并提供实时的设计回馈,或可直接套用 Kulicke & Soffa 所验证过的定义档,以确定所设计出的 wirebond 都能够真正被生产实现。

对于 Bump (凸块) 和 pillar (支柱) 的连接,设计人员可用自动和半自动工具来建立这些经过验证的架构,快速套用在DIE上,以符合当今高密度封装设计需求。

全自动的 BUMP-TO-PACKAGE 接点设定和布线完成率评估

除了支持使用传统线路图和 netlist-based 的逻辑定义之外,利用 OrbitIO 互连设计器进行前期跨架构的系统规划,或是利用 SiP Digital Architect 下的 System Connectivity Manager 的独特系统连接管理器,都可以很有效的规划及分配总体的联机关系。逻辑关系也可手动直接定义,或者是套用现有设计规范下,以最好的走线等的不同模式架构下做最适当的自动布线考虑并定义出其联机关系,如将各信号会依照规范及空间做信号的指定,差动信号的 BUMP 也会照封装接点选择最好的位置选择,而 net-per-layer 也可清楚的看到所有信号的分布状态。另外,route planning 的 flow 和 bundles 对整组信号分类和视觉上效果,对于高速信号规划会更有帮助。

手动 / 半自动和自动布线

Allegro X Advanced Package Designer 和 SiP Layout Option 集成了一套基于规则的半自动和的自动布线功能,让我们面对无论是任意角度、单层、Wirebond 还是增层结构上多加的 silicon interposer 等任何类型的 IC 封装设计,都在确保其可制造性之下能快速准确地完成布线设计。

HDI 高密度设计

HDI 高密度或增层式的设计也广泛地应用在封装设计中,以求最有效的层面利用及配合细小间距的 flip chip 需求。Allegro X Advanced Package Designer 能搭配其完整的 HDI 规范以达到其自动辅助设计的目的,而微导孔 (microvia) 的充分支持和自动设定,并可做合并及分离等编辑,让层面的利用率最高并符合生产需求,以达成设计和生产的共同目标。

切图设计

若欲执行完整功能,需加购 Symphony Team Design Option

Cadence 提供了多个使用者或同步的设计环境,加速设计时效、加快上市时程。

其中 Partition 可将整份设计依其区块或层面切分给多个使用者,而使用者可查看别区块的的最后更新结果加以配合调整,进而压缩整份设计的总体设计时程。

还有同步的 Symphony,可让多个设计人员在同一时间同时操作同一个设计进行工作,而无需分区设置。当加入的布线工程师越多,完成布线的速度就可越快。在布线的同时,可以引用 Allegro X Advanced Package Designer 和 SiP Layout Option 内的各项功能,如强大的铺铜编辑或 Allegro auto-interactive phase tune (AiPT),和 auto-interactive delay tune (AiDT) 等自动 Tune 线的功能加速设计完成 。

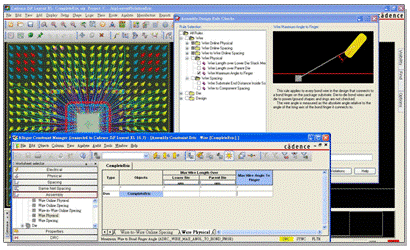

DesignTrue DFM 和 ARC 检查

( 仅包含基本检查,完整检查仍需加 SIP Layout Option )

Constraint Manager 中有全面的 design for manufacturing (DFM) 制造设计检查功能,若有 SIP Layout Option,其中另外有的 assembly rule checker (ARC) 提供了数百种检查来满足制造上的要求 (非传统 DRC 的间距检查)。其检查项目可把这些规则加以分类或单独指定或是自定义选择来执行,最终的检查也会显示在 Constraint Manager 的 DRC 页面中及图档上。

多元的生产制程资料准备

在生产制程的准备方面,而从文件到生产的各种数据都十分完备。可以很快速地建立出打线数据、尺寸标注、所需图样和封装数据,或如镀金棒 (plating bar)、蚀断线 (etchback plating)、透气孔 (metal pour degassing) 和铜箔平均化 (metal layer balancing) 等等都有考虑。为了搭配后段的生产检查甚或 SI 分析,所支持的输出格式包括有 Gerber、IPC2581、DXF、AIF2 及 GDSII 等。如果有 SIP Layout Option,还能利用 design variants 功能来定义出不同零件搭配组合的 BOM。另外,大多数的封装厂也都是使用 Cadence 的 PACKAGE 产品,所以若情况许可也可将设计图档直接给封装厂,让此数据在不破坏原始规范的情况下做更细的生产参数微调,以提高产出的良率。

对于 PCB 系统阶的数据传递

Allegro X Advanced Package Designer 工具不只能连结 silicon 与 package 设计,也能连结 package 与 PCB 设计。对 PCB 所需的 floor planning 规划跟 layout 的相关数据,也能自动建立出所需的实体零件、线路图 symbol、跟 device 模型。您也能够萃出 Die 或 BGA 的数据到 Excel 格式的电子表格中,以加速设定时间并提高其准确率。

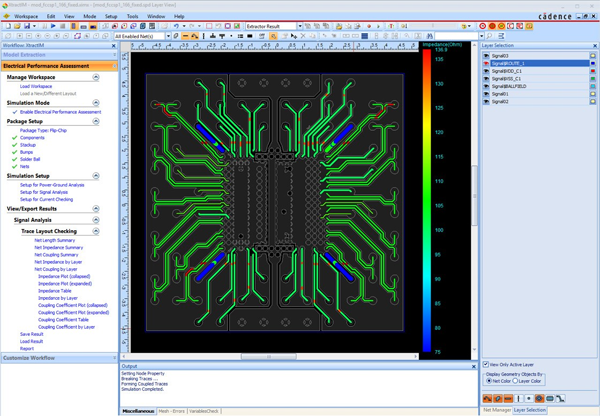

封装设计的信号和电源分析

借助 Cadence 的 Clarity™ 和 Celsius™ 技术,可以进行详细的布线萃取和 3D 封装建模,以及具电源考虑的信号完整性和热的分析。这些功能使封装分析和建模解决方案能够在早期的设计时间就能开始进行特性评估以及 DC/AC PDN 分析,进而到最后使用 Hybrid EM 混合求解器来萃取完整封装模型,或使用全波 3D 求解器来萃取更详细封装模型。

您可以依需求做以下检查:

封装设计特性评估,可快速检测有问题的封装设计数据,包括检测封装引脚是否有过多的电感效应、不适当的阻抗和耦合等 |

|

含电源考虑的混合求解器萃取,可考虑 PDN 及信号的耦合并进行 RLGC 和 S 参数的模型萃取 |

|

全波 3D 求解器 - 解析封装设计内部详细结构用于高频布线模型萃取 |

|

IR-Drop 分析 - 同时考虑布线和零件效应的电 / 热协同模拟,及不同区块的温度分布和铺铜 / 贯孔 / 走线间的电流密度计算 |

封装性能评估可以在实际布线的早期阶段开始,而不需等到最后才可执行。利用初始的联机关系进行可行性研究,例如考虑 DC 的 IR-Drop 和电流的最佳迭构 / 规范以及信号的拓扑架构,可帮助确定最终的封装类型并以最低的成本达到最佳的电气性能。随着封装设计的继续,可以萃取信号和 PDN 的模型,以考虑 RLC 的寄生效应和信号的阻抗和串扰,或 insertion 和 return losses 的关键特性。

还可搭配现行大多数 OSAT 和 Foundry 所使用的 Cadence 封装设计技术,来探索散热方面的考虑。利用这种互操作性,当设计达到最后阶段时能够互相搭配交换电热分析数据,以执行更完整的封装评估 (包括 IR-Drop) 和模型萃取,并生成最终的 HTML 报告,以确保实时发现重大问题并完整记录设计。

若是会在高频下运行的封装设计,可以在关键封装区域执行全波 3D 萃取以确保能满足高速信号的性能规格。

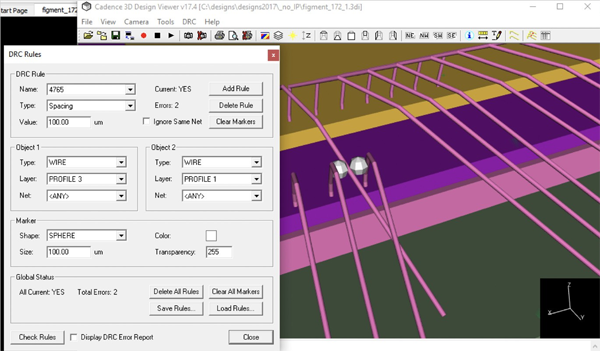

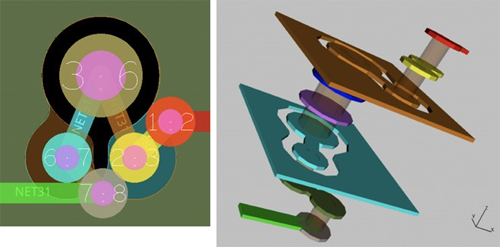

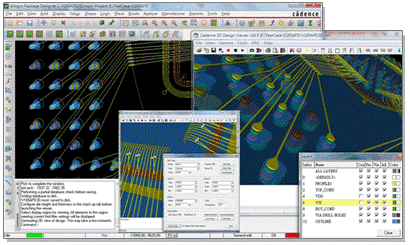

3D 设计视图功能

Cadence 3D Design Viewer 用于复杂的 IC 封装设计检查,是一个完整的实体 3D 模型检测器和 3D Wirebond DRC 解决方案,现已包含在 Allegro X Advanced Package Designer 中。它为跨团队设计的审查提供了共同的平台让用户可查看和研究整个设计,如在具有多重 Wirebond 结构的封装设计下,选定的最佳 Wirebond Profile 打线定义的组合效果。

智慧 3D 设计视图

尽管 2D 显示非常适合于基板布局、布线规划和金属铺面等绘制,但 2D 的效果并不适合用于复杂芯片立体堆栈和 3D 集成的设计 / 管理或验证,封装设计的复杂性和密高度的要求更显出 3D 的重要性。 利用 Cadence 3D Design Viewer 使封装设计人员能够以 3D 的方式,查看其实际设计来满足此需求。设计人员可以交互式的缩放 / 平移 / 旋转 3D 视图,或是从一组预定的视角效果中进行选择。

互动标记

在查看 3D 设计期间,工程师可以为设计审查或设计资料建出 “Markup” 标记快照,其中包括添加基本图形、箭头和文字的功能,这对于与设计伙伴间的集成,以及测试和装配制造部门进行沟通时,特别有用。

3D Wirebond 间距检查

在 Allegro X Advanced Package Designer 设计中,可定义和储存其 3D 检查规则。您可自行定义这些规则来检查设计中 Wire 导线,和零件之间的 3D 间距。