全球最多人使用的设计输入方案

Cadence® OrCAD™ X Capture 原理图输入系统具有快捷、通用的设计输入能力,为全球最广受欢迎的设计输入工具。它针对设计一个新的电子电路、修改现有的一个 PCB 的原理图或者绘制一个 VHDL 模块的方框图都提供了所需要的全部功能,并能迅速验证您的设计。

Cadence OrCAD X Capture 作为设计输入工具,运行在 PC 平台,用于 FPGA 、 PCB 和 Cadence® OrCAD™ PSpice® 设计应用中,是业界第一个真正基于 Windows 环境的原理图输入程序,易于使用的功能及特点已使其成为原理图输入的工业标准。

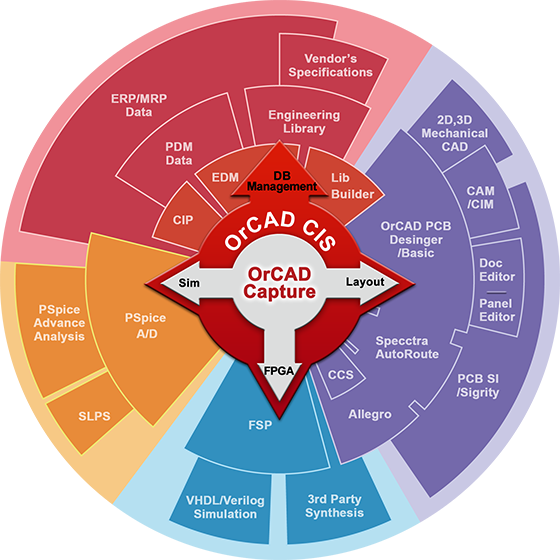

OrCAD 产品关系图

1. 单一化的设计窗口

OrCAD™ X Capture 的电路设计可支持从最简单到最复杂的平面或分层设计,并且可经由网络表连接Cadence® OrCAD™ PCB Editor、Cadence® Allegro® 或其它的 Layout 软件来完成 PCB 设计;也集成了 PSpice 与 VHDL (NC Verilog) 的环境---提供您做仿真与数字 (FPGA Design Flow) 前端设计平台。另外也可以配合 OrCAD PCB SI 与 Cadence® Allegro® SI 来解决高频问题。

2. 利用 Windows 操作接口可以更方便的编辑与分享彼此的构想

OrCAD X Capture 利用 Windows 简易操作的观念,可用剪下、复制、贴上等等的特色来操作;也可以利用 Windows 的多重编辑方式来编辑两个以上的原理图或是由另外的档案复制数据过来使用。

3. 支持广大的 PCB 应用

OrCAD X Capture 可以支持 30 种以上 PCB Layout 软件的网络表格式,包含 OrCAD PCB Editor、Allegro、Pads、PCAD 200X、Protel、Mentor Graphics BoardStation…等等。

4. 集成了 Cadence 其他系统程序来处理不同的需求

OrCAD X Capture 是 OrCAD PSpice、OrCAD PCB SI、OrCAD PCB Editor、Allegro 与 Allegro SI 的设计前台。透过网络表 (netlist) 的连接,可利用它同时标示出彼此的关联处 (cross-highlighting),也可直接作为测试的信号源 (cross-probing)。而利用 Back Annotate 的功能,可将 Layout 序号或 Constraint Manager 的变化回馈到 Capture 的原理图中。

5. 提供多重的 PLD 设计组件与方式

OrCAD X Capture 提供六种 PLD 使用原理图的元件,包含 Xilinx、Altera、Actel、Lattice、Lucent 与 Atmel 六种 Vendor 的元件,这些元件允许您利用 OrCAD X Capture 来做为设计 PLD 的前台。

6. 可以利用 OrCAD X Capture 来完成不同的仿真并提供广大的 PCB 网络表格式

可以利用 OrCAD X Capture 集成的环境,来完成 FPGA Design Flow 的设计 - 仿真、合成、布局的功能。并绘制完整的原理图来连接 PCB Layout 软件,以完成一个项目设计。

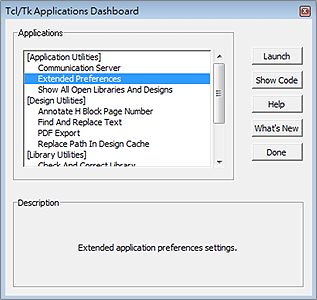

7. 可以利用 OrCAD X Capture Tcl/Tk 程序接口开发新的操作功能

可以利用 OrCAD X Capture Tcl/Tk 程序,来开发或者外挂新的软件操作或检查功能让 OrCAD X Capture 更易于使用。

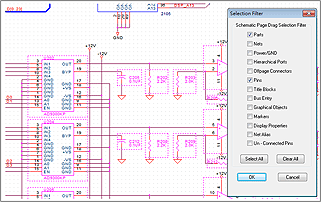

物件选择功能,可筛选物件类型

在选择物件时,可利用鼠标右键的 "Selection Filter" 设定可选择的物件类型,例如您只想框选原理图中的元件与 Pin,就可以先全部清除只留 Parts 和 Pins 再用鼠标框选后,就只会选取范围中的 Parts 和 Pins,而不会选取到其他对象如 Nets 或其他物件。

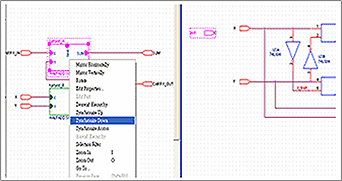

阶层式电路,同步产生 / 删除所对应的连接符号

在绘制阶层式电路时,如果上层的模块图有接点的更新或是下阶的细部线路有任何外接接点的增减。在以往您需设定好相对应的名称才会有其接续性,现在 Cadence® OrCAD™ 会自动依接点的增减自动设定好阶层式电路上下阶之间的对应关系,方便阶层式电路的实际应用。

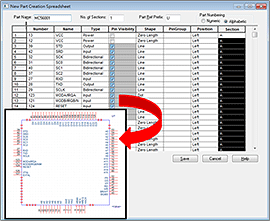

從空白表格中直接 建立零件

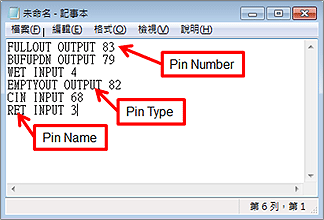

在建立零件时最大的困难可能是要建入数百个 PIN 的 Pin 脚号及名称,现在可以从收到的规格表中撷取所要的 Pin 脚号及名称,贴入 OrCAD 中再定义其他的相关讯息,如 Pin 脚所在的位置等等,可快速自动建立出此颗零件。

依照原理图页面指定零件序号编排

如果可由 IC 厂商,如 Xilinx 得到 零件的 Pin 脚数据文件,可稍做整理后理出具有 Pin 脚名称、Pin 脚种类、Pin 脚号的文本文件,Generate Part 加载此文件后自动建立出 OrCAD 的零件,不必再用传统方法逐一宣告,大量缩短建立零件的时间。

切割大颗零件

使用表格方法或 Pin File 的方式自动建立零件,要是输入的 Pin 脚数太多可能会建出一颗超大的零件,因为大过图框而不适合放到图面上,如果想把大颗零件切割成几颗小的非同类零件,可用 Split Part 定义出切割后的小零件数量及各 Pin 脚所在的位置后自动生成各个非同类零件。

Cadence OrCAD 与 Cadence Allegro 集成

除了可以在 OrCAD 原理图上直接定义 Cadence® Allegro® 零件相关属性,如 ROOM 、 Fixed 、 BOM ignore 、 …..,也可定义 Allegro 信号属性,如 MIN_LINE_WIDTH 、 MAX_VIA_COUNT 、 …… ,现在甚至要定义 PIN PAIR 所指定的 U1.17 到 U2.5 的 PROPOGATION_DELAY 的线长,都可在 OrCAD 原理图中轻易实现。

定义差分信号

在绘图时也可直接定义差分信号名称及其组成的线对成员,或用 Auto Setup 定义信号名称规则 (如后缀是+和 - ) 即可由程序自动辨识定义出各个差分信号对。

能将 OrCAD 原理图上对 Allegro 的零件或信号宣告的属性 (properties) 以 PCB Editor 方式或用传统 OrCAD 转 Allegro 的方法以附带 properties 的方式转到 Allegro 中

专案压缩

在绘图完成后,可利用 Archive Project 选择要压缩的相关文件类型及其文件名和路径,也可把外部的文件,如零件规格、相关程序代码等等一起压缩成 .ZIP 文件,在项目的管理和备份上更加便利。

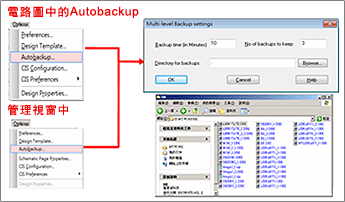

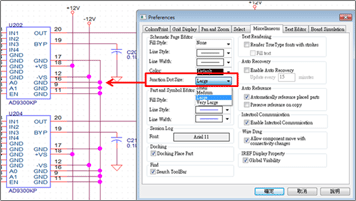

可以设定自动备份的路径、时间间隔及数量,程序会自动存成各个 .DBK 的备份文件

原理图设定备份文件自动存盘,可协助工程师快速地回复前一段时间所修改的数据。

OrCAD 可依照原理图的页码设定每页起始的零件序号及最大的零件序号

原理图零件序号可依照原理图的页面顺序设定起始值及最大值,当零件序号要重新排列,将以设定好的范围做零件序号的编排!

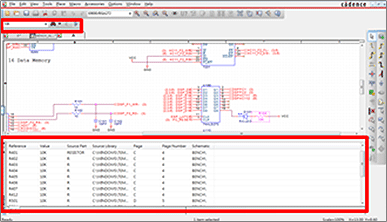

物件搜寻

更加方便的物件搜寻功能,当物件搜寻后,将在画面下方有 Find window,使用者可透过搜寻结果点选物件,原理图将直接切换并且高亮显示所指定物件。

原理图 Junction (节点)大小改变 - 可透过 Junction Dot Size change 的功能更改原理图节点的大小

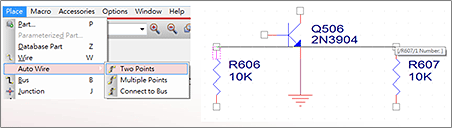

Auto wire 自动连线功能

原理图 Net 自动连接功能,可让使用者快速的做单点对单点 Net 的连接,或单点对多点同时连接,或是针对 BUS 线路的连接!

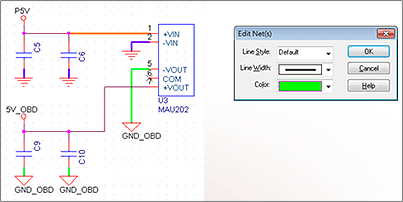

原理图 Net 查找功能,可针对原理图中所有与点选的 Net 相同的线段全部列出,并透过点选的方式可以跳转到相对应的页面中

原理图线段颜色及宽度的改变,可针对原理图重要的 Net 线改变其颜色、线宽、线型

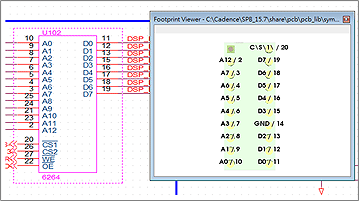

Footprint Viewer 可在原理图或零件库编辑画面中,显示所对应的 Allegro Footprint 形状及引脚数量 (Pin number) 和 引脚名称 (Pin Name) 的位置

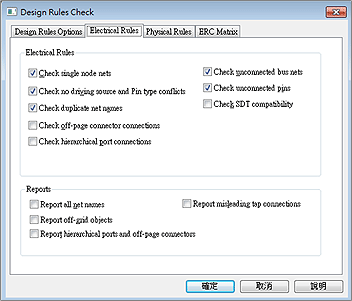

Design Rules Check 检查的更新

原理图 Design Rule Check 检查的更新,现在分成含有电气属性的检查及不含电气属性检查两大部分,并且在检查项目中增加了重复 Net name、Footprint missing、未摆放的复合式零件 Package 等重点检查或报告项目。

Tcl/Tk 程序支持

OrCAD X Capture/CIS 开始 Tcl/Tk 程序的支持,可以自行开发程序或是到原厂 Markeplace 网站下载 OrCAD X Capture/CIS Utility 挂载到程序中使用!

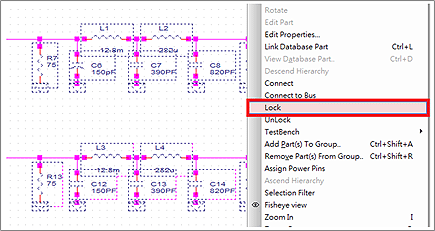

原理图锁定功能,原理图可将部分区块或整页原理图物件锁定 (Lock),锁定的物件将不可移动或删除