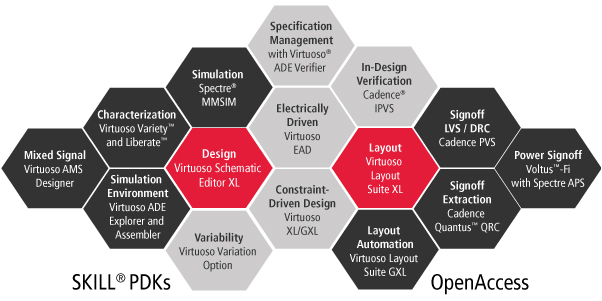

Custom Design Platform

个人消费电子和无线产品已经成为当今世界电子市场的主导力量。这些设备对于新功能 (new features) 和特性 (functionality) 的要求,促进了 RF、模拟和混合信号应用设备的前所未有的发展。为创造满足该需求的新产品,企业采用 Custom Design 的技术,将可使 IC 设计工程师更能掌握精确的仿真数值,如电压、电流、电荷,以及电阻与电容等参数值的持续比率。

为了简化设计 Custom IC 的流程,并将其集成到终端产品中,半导体和系统公司需要精密的软件和设计流程方法,以达成迅速上市和迅速量产的目标。Cadence® Virtuoso® Custom Design Platform 提供了极其迅速而保证芯片精确的方式,进行定制仿类比、RF 和混合信号 IC 的设计。

Cadence® Virtuoso® Custom Design Platform L 是入门级的客制 IC 专业平台,不论您的 IC 是应用在类比或是混模信号的设计,Virtuoso 平台都能提供您一个从前端到后段的集成流程,以及各种不同程度的解决方案以符合各种客制 IC 不同的设计需求。

VIRTUOSO SCHEMATIC EDITOR L

快速精确的线路输入 Virtuoso

Schematic Editor L 的强大功能提供您快速易用的设计输入环境,利用其完备的的元件库使得 gate 和 transistor levels 的设计更加快速,再加上便利的接线功能,使我们面对更大更复杂的设计时能更加顺手。除此之外,阶层式编辑器能方便地管理其阶层的关系,当您的设计是规划成阶层式的结构时,也能确保整体设计中所有接线的正确性。

业界标准的设计语言

利用业界的两种先进的硬件描述语言 VHDL 和 Verilog HDL,Virtuoso Schematic Editor L 可方便地套用到 mixed-level 混合设计中,另外也支持了 Verilog-AMS 及 VHDL-AMS,藉此我们可以不论设计类型,以同样的方式来设计 mixed-signal 混合信号,还能由输入描述语言自动建立所代表的线路区块,以供 system-level 系统阶的 IC 设计需求。此外由于现今 IC 设计不单单只考虑到芯片内部的效应,对于 PCB 载板上的 RDL 走线与组件,都需要同时考虑,因此现在我们也同样支持 PSPICE 的描述语言,使得产品设计能够通泛考虑的更加全面与完整。

扩展的设计检查功能

为了要确认设计的精确性,我们可以自定义对图面和电性规则的检查条件,例如零件重迭、短断路、未接的 inputs outputs、对象的一致性或不合的名称等,让设计者以单一指令完成对单 / 多张图面或是整体阶层设计的 pin name 对应和接线的完整性及信号编名的检查功能。

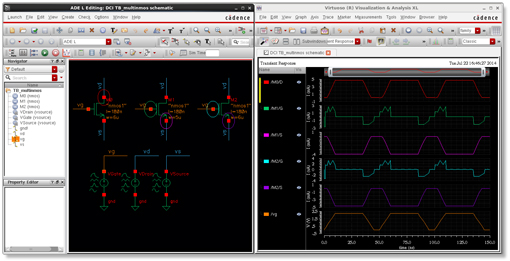

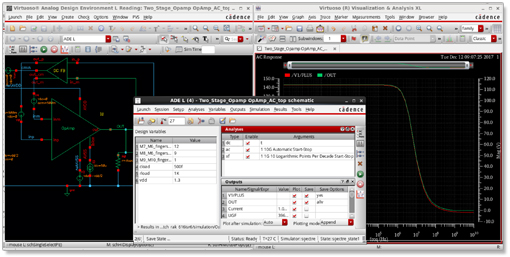

VIRTUOSO ANALOG DESIGN ENVIRONMENT L

易用互动的设计和仿真环境

Analog Design Environment L 的交互式环境可让我们设定、执行 Multi-Mode Sim 和分析其结果,利用其各种显示及分析功能让您对仿真、射频及混和信号的掌握更加便利,期望让您能更快速找到设计中的关键点,并能求得优化的结果。另外,其多样的环境除了搭配之外,再配合其他仿真程序时,不需要重新设定所有参数。

内建波形显示及信号分析

波形显示内建了可扩展的波形计算器,提供了完整的 post-sim 分析环境,其波形显示窗口可显示各种仿真和混和信号数据,如 noise、corner、射频波形,另外还可调整显示的效果,如水平 / 垂直轴、波形颜色、标注等,建立出最好的图面及报表。波形标签及计算器可精确量测出在 Transient、AC 与 RF 等不同模式下的信号,并可依输入 / 出电压值或电流值再搭配代数运算以求出其他的量测结果。

跨越线路和实体设计的鸿沟

Virtuoso Analog Design Environment L 所提供的仿真环境可比对 pre-sim 及 post-sim 的不同条件,使得我们可以跨越线路设计和实体布局的障碍,实现由前端到后段完整的 IC 设计流程。

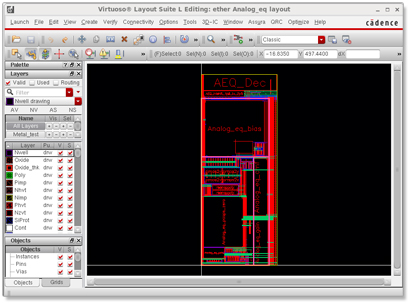

VIRTUOSO LAYOUT SUITE L

全阶层式、多窗式的设计环境

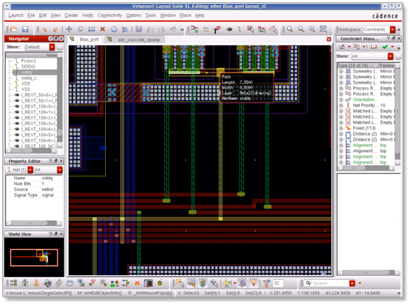

Virtuoso Layout Suite L 可在一个编辑环境中同时开启多个 cells 或 blocks 甚或是阶层均可在同一窗口打开,说明设计者在复杂的设计中确认其数据的完整性,其集成的 World Viewer 全窗口可以很直觉地查看整个设计中相应区块的位置,并可执行选取、显示范围调整、重绘等常用指令,以提升布线效率。

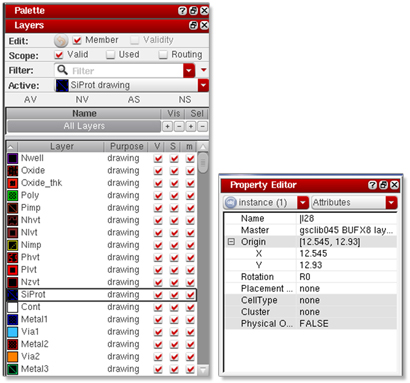

多样的参数式 Cells 加速设计时效减少设计错误

Parameterized cells (Pcells) 提供设计自动化的效能以减少繁琐及重复的布图工作,Pcells 可在不更动最原始 cell 的情况下更改每个 cell 的尺寸、SHAPE 及所含对象,依参数设定所建立、编辑和管理的 shapes 和 devices 可更加简化,以加速布图效率并减少设计错误。

QuickCell 选单自动建立 Device

QuickCell (QCells) 参数选单功能可快速建立及编辑 Pcells devices,可在无 Pcells SKILL 的环境下实现建立及编辑 devices 的环境, 由于 QCells 是 “C” 为基础的环境,所以可程序的 Pcells SKILL 也可套用及兼容于 QCells 的环境下。

设计规范管控以增加效率

Virtuoso Layout Suite 提供 “设计规范管控”的功能,可以实时监控违反规范的错误,以增加布图效率减少错误点及侦错的时间,也支持 90 纳米 (或更小) 的各种复杂制程规范的 technology file。

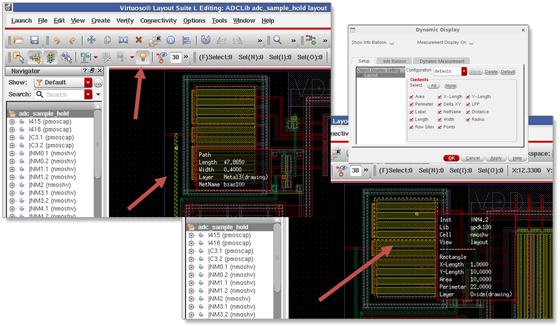

自动简化及优化的布线效果

Virtuoso Layout Suite 能够自动简化及优化 block 来达到以 ”设计规范管控” 的功能和流程,“动态量测” 省掉许多手动量测的麻烦,”对齐功能” 也能加快对齐图型、接点和对象的效率,”信号标示” 让您在多阶的设计中达成对信号查询,明亮显示及检查接续性目的。

Multi useful Assistants window

View all geometry dynamically during editing commands

Design Rule Driven - Real time aware DRC violations

Cadence® Virtuoso® Custom Design Platform XL 系列是客制 IC 的进阶平台,提供您在设计更高阶产品的更好环境,包括的产品有 Virtuoso Schematic Editor XL、Virtuoso Analog Design Environment XL、Virtuoso Layout Suite XL。

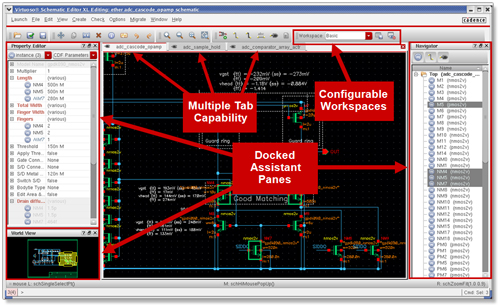

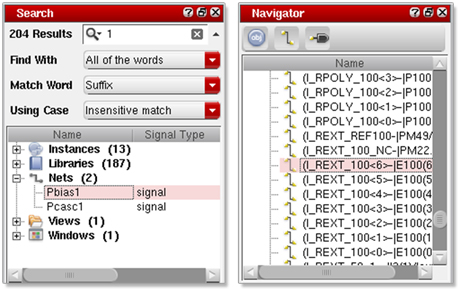

Virtuoso Schematic Editor XL

提供进阶功能使得其效能达原 Virtuoso platform L 的五倍之多,使用者可利用其 design constraints 设计规范来串连整个设计,这些规范可让使用者从线路图端即宣告布图的重点和注意事项,如匹配性及对称性等等。

作为 Virtuoso 的前端平台,Virtuoso Schematic Editor XL 提供了客制 IC 设计输入端的各种扩展功能,从业界标准语言 (如 VerilogR 、VHDL 和 C) 所做的架构定义 architectural definition 到 transistor level的最终结构定义,都能说明工程师执行设计中的每个阶段,利用 XL 阶所介绍的 “design constraints” 概念,让我们可以将设计的 ”意念” 储存在设计之中,若下一次设计有使用,可直接套用,减少其间的落差。

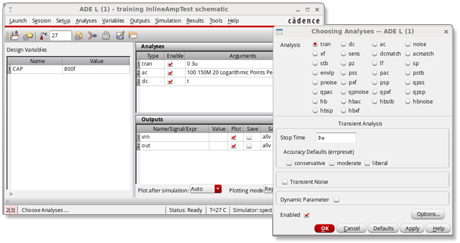

Virtuoso Analog Design Environment XL

Virtuoso 平台上最先进的设计和仿真环境,经由跨设计的对象指定及选取效果,可帮您建立一个快速且精确的设计验证环境。

Virtuoso Analog Design Environment XL 可以在一个易用的工具中同时管理及验证多个 design,并且在设计和验证的流程中,所有线路可以对应到相应对象成功 / 失败的状态。另外,所有的 sweeps、corners、Monte Carlo 及量测都能被管理及储存在一个位置中,以求快速准确的设计验证。

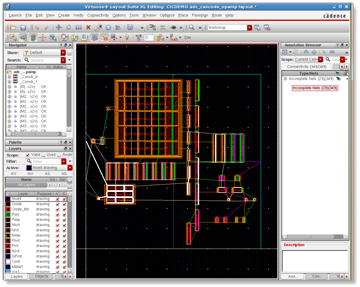

Virtuoso Layout Suite XL

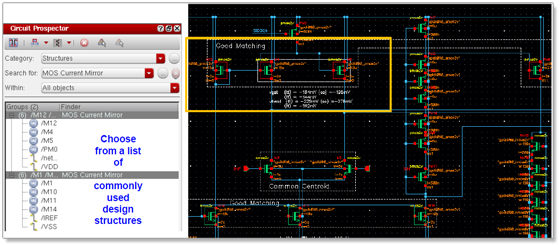

Virtuoso 平台上最先进的客制布局环境,提供了 constraint-driven 规范-管控及线路图-管控的两种实体布局环境,让您在设计数字、混和信号及仿真产品时的 device、cell 和 block 阶都能有最好的规范可依循。

作为 Virtuoso 的高阶布图平台,Virtuoso Layout Suite XL 除了 L 阶的基本 polygon 布图编辑功能之外,更针对 device、cell 及 block 来提供客制数字、混和信号和仿真设计等支持,也使得规范管控及设计管控的功能能够与其他自动化的进阶功能相结合,以加速客制零件编写的速度,别忘了还有 parameterized cell (Pcell) 和 SKILL 可让您在 device 的建立和编辑时更能得心应手。

软 件 特 点

快速且精确的设计输入环境

Virtuoso Schematic Editor XL 提供了 L 阶中的搜寻、属性编辑查看和设计阶层环境等各项功能外,也可将电路设计输出至网页浏览器中查阅,另可使用 Design Constraints 设计规范来串连整个设计,这些规范可让使用者从线路图端即宣告布图的重点和注意事项,如匹配性及对称性等等…快速且易用的设计输入功能。

规格式的设计

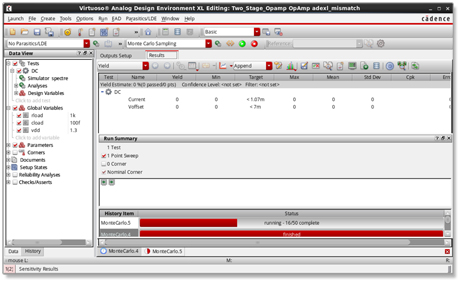

通常规格需要多项测试,并经由结合测试规范与具体测量来加以确认,为了要加速设计的验证,Virtuoso Analog Design Environment XL 将设计管理及规格输入结合在同一个环境中,让您可轻易地建立多种情况下的不同测试条件以验证您的设计。

而在 project 内,可选取所有的测试 sweeps、corners 和相关档作验证比对之用,并可查看项目的所有测试结果,如所有的波形、量测值和仿真档的状态都可以呈现出来。

Virtuoso Analog Design Environment XL 可执行单一或多个测试亦或是多个测试中的 sweeps、corners 及 Monte Carlo 分析,可使用并行处理的选项让整个仿真管理上更加有效率。

Virtuoso Analog Design Environment XL 支持将所有测试分析结果自动储存作规格确认之用,亦可集成 Virtuoso Multi-Mode Simulation 实现仿真、射频、混合信号的仿真验证。

联机管控式的功能加速设计的完成时效

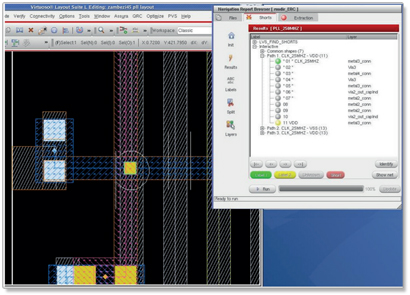

Virtuoso Layout Suite XL 设立了工业标准,改变传统的客制设计流程,设计者可经由 Virtuoso Schematic Editor XL 所定的联机关系,或是由外部,如 CDL 或 SPICE 所加载的联机档来执行实时的 LVS,用以检验其布图,也因此实现了 ”correct-by-construction” 的布图环境,提高生产力并减少验证的时程。另外,也使得繁琐的 DEVICE 建立、摆放和布图可以自动化,线路图也可以跟实际布图之间的 instances 和 devices 互相查询、highlight,并可快速找到未接的信号等其他功能。

规范管控及设计管控以提高生产力

Virtuoso Layout Suite XL 提供规范定义及管理环境,另外,设计规则的定义还可自动且实时地标示违反设计规则点,让我们可以同时达到依规范管控布图及提高生产力,并减少布图错误点和验证的时间,不论是传统仿真的 .25u 到最先进的 45 纳米制程的条件,所有 Device 建立、摆放、或自动 / 手动布线,都会遵照规范内的 technology file 的规则定义。

与其他 VIRTUOSO 平台工具的密切集成

上述的功能都集成在 Virtuoso 客制设计平台上,可以利用单一环境集成平台上的所有功能来建立分析及实现不同面向,如 ASICs、可程序 IC、MCM、数字 IC、仿真 IC 及混和信号 IC 的设计需求,VIRTUOSO 平台支持业界标准的 OpenAccess (OA) 数据库及 Cadence SKILL 可程序语言,让您可以自定义工作环境建立最佳的自有环境及流程。

设计流程

线路设计 Circuit design (Front End)

Cadence 的线路设计 circuit design 方案可让您快速且精确的绘制出您的设计概念并有效管理设计的方向,尤其是在客制 IC 的设计流程中利用对非重要信号的自动化步骤使得工程师可以专注在极精细的设计中,利用其 Analog Design Environment 可以从线路图直接对应到仿真 analog、射频 RF 或混合信号 mixed-signal 的不同设计所引发的线路特性上的不同效应。

其工具有 :

Virtuoso Schematic Editor |

|

Virtuoso Analog Design Environment (ADE) |

仿真 Simulation

分别有 Block-level、Chip-level 和 Mixed-signal 的不同仿真效果和工具:

Block-level |

小功能区块的仿真,主要着重在单一区块从架构到功能的实现 |

|---|---|

Chip-level |

集成所有区块的全芯片仿真,着重在其效益和准确性,由其是 system-on-chip 时因集成仿真及数字区块所衍生出其间的互应及影响 |

Mixed-signal |

综合 block-level 和 full-chip 的类比仿真器和先进的数字分析模拟器,使得我们可以把多种语言的数字设计可以跟仿真或 RF 轻易的集成在一起 |

其工具有 :

Virtuoso Multi-Mode Simulation (MMSim) |

|

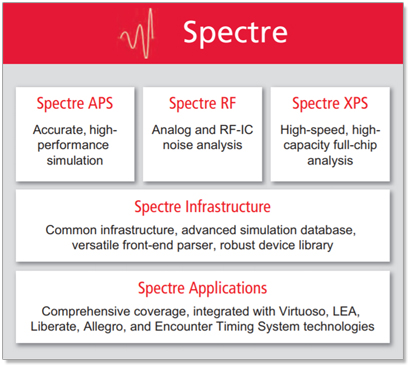

Spectre Circuit Simulator (Spectre) |

|

Spectre Accelerated Parallel Simulator (APS) |

|

Spectre Extensive Partitioned Simulator (XPS) |

|

Virtuoso UltraSim Simulator (UltraSim) |

|

AMS Designer Simulator (AMS) |

布局设计及布线 Physical layout & Router (Back End)

布局设计主要是将前端原理图转换为实际的芯片布线,最终将布局图转换为光罩档,以供晶圆厂生产。客制化的布局需考虑许多的布局条件,往往需要人工来完成,Cadence 的布局工具提供方便的功能,可让工程师加快布局的速度。

其工具有 :

Virtuoso Layout Suite |

|

Virtuoso Chip Assembly Router (CAR) |

|

设计验证 Verification

布局图完成后,需检查是否符合制造的设计规范,以防止如芯片线路短路或断路…等等的影响。另外亦需比对布局图与原理图是否一致。

其工具有 :

Cadence Physical Verification System (PVS) |

|

Assura Physical Verification (ASSURA) |

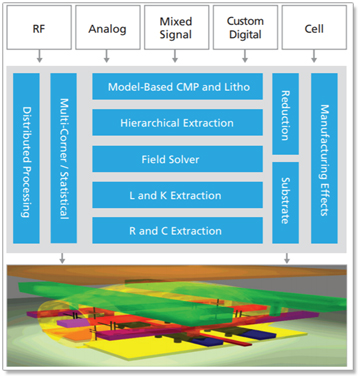

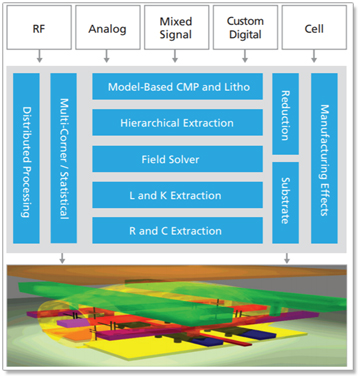

萃取寄生效应 Parasitic Extraction

寄生效应会造成我们设计的问题,通过 Cadence QRC Extraction 萃取寄生效应,并藉由 Virtuoso Solution 将萃取出寄生数据的响应到设计上,让我们对整个设计有最全面和宏观的考虑跟最实时的分析,以判定出真正问题之所在。

其工具有 :

加速客制化 IC 布局工具 SKILLCAD

SKILLCAD 是一家专精于发展加速客制化 IC 布局工具的软件公司;SKILLCAD 的系列产品集成了 8 种主要的工具,这些工具可以支持先进纳米制程的设计规则;SKILLCAD 软件公司是 Cadence 优秀的策略伙伴,其产品主要是建构在 Cadence Virtuoso 的平台上,增广 Virtuoso 在不同产业的应用范围,并有效缩短芯片布局的时间。