By Tyler Lockman, Cadence

銳角,無論是在澆注的鋪銅中產生尖銳棱角,還是在兩塊不同的金屬之間形成銳角,都是一個棘手的問題。作為設計師,我們會不遺餘力地嘗試避免上述情況;但是儘管付出諸多努力,銳角還是會悄然出現在設計中。

那麼,如何才能在對佈線層進行最小改動的情況下,有效地擺脫設計中的這些問題呢?倒圓角淚滴是一種一階的修復方法。您可能會發現,銳角不只是出現在焊盤和走線的交叉處。

本文透過 Cadence Allegro® Package Designer Plus Silicon Layout Option 17.4 版本的演示,為大家講解自動修復銳角的操作方法。

將板的銳邊歸類為銳角

對於已澆注的平面鋪銅,近似直角是可以接受的。從技術上講,89.5 度小於 90 度,是銳角。佈局中的所有頂點都必須緊扣資料庫製造網格。正因如此,Allegro 產品預設為銳角提供了 1 度的容差範圍 (除非是在嚴格的正交環境中工作,即使 45 度的轉彎也往往是不精確的)。這意味著,直角被認為是 89 至 91 度之間的任何角度。

對於有機基板,這個容差通常綽綽有餘。然而,對於矽設計,可能擁有更嚴格的規則,規定任何小於 90 度的角度都應該被修剪掉,無論差別多麼細微。

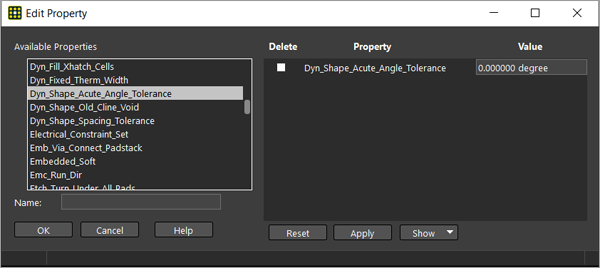

曾經,Cadence Allegro layout 工具有一個環境變數,可以用來調整這個容差。如下圖所示,shape_right_angle_tolerance 變數用於控制這類銳角的「誤差範圍」。

不過從 17.4 版本開始,這個變數被一個設計級別的屬性所取代。透過在資料庫層面進行控制,無論誰在編輯或它們的環境是如何配置的,都可以保證設計的鋪銅行為保持一致 (如果打開設計時已在環境中設置了環境變數,那麼該變數的值將被用來在幕後設定該屬性)。

對於矽基板來說,把該容差設置為零將確保設計符合正式簽核規則。這並不是要求將動態挖銅參數從圓角切換到全圓角。全圓角會讓直角變平滑,例如方形焊盤周圍的空隙。然而,如果容差為零,將不會對真正的 90 度角進行圓角處理。

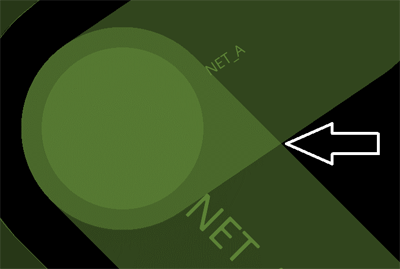

上圖中的垂直線段向右微微彎曲,形成一個銳角。預設的 1 度容差不會導致 cline 彎曲內側的形狀變圓。但是,如果需要的話,0 度的容差會帶來一個平滑的圓形過渡。您是否需要嚴格避免銳角,還是與 cline 邊緣的距離保持一致更為重要?對此您可以諮詢製造商,他們可以幫助您做出決定。

去除銳角

我們已經瞭解了正平面鋪銅以及去除金屬的尖銳區域,剩下的就是與之相反的情況:金屬的急彎,導致邊緣之間存在狹窄區域。我們在此討論的是:

這的確是一個問題,因為我們從來沒有打算製造急彎,但這種情況仍有可能在意料之外發生。在任何兩塊金屬之間都有可能產生這樣的情況 —— 引腳和 cline 直線、過孔和鋪銅,甚至如果兩個焊盤靠得很近的話,這個問題也會在其之間出現。

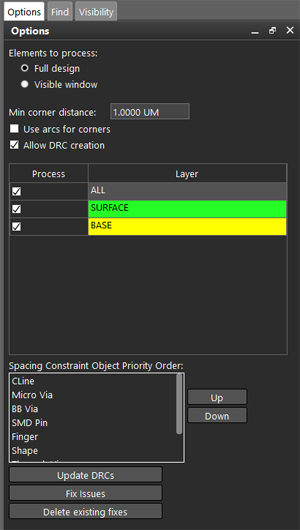

雖然 Allegro Package Designer 工具中早已包含針對銳角的裝配 DRC 檢查,但 Silicon Layout Option 增加了自動修復功能。在 DRC 錯誤標識工具的支援下,自動修復工具將在這些區域添加少量的金屬,以實現平滑過渡。請看下面的介面:

在大多數情況下,我們可能需要在設計中的所有導體層上進行這種修復。但是,我們需要做出的最重要的決定是:想讓修復工具添加多少金屬 (最小角距),以及系統是否可以使用弧線,還是必須為彎曲製造倒角。這一選擇可能主要取決於製造輸出格式。

最後在上圖介面中,有一個重要的物件類型列表。這個清單用於控制資料庫將平滑物件看作是什麼類型的物件。在優先清單中,對於兩個元素之間的每個銳角修正形狀,列表中排名靠前的元素類型就是將該形狀視為的類型。

通常大於鋪銅到線的間距。那麼,透過將銳角修復工具作為 cline 來處理,動態空隙將減少對附近鋪銅的影響,並允許過孔、引腳和其他走線更接近該鋪銅。

當我們在倒角和弧形風格的角之間進行挑選時,可以看到以下區別:

弧形將提供一個漸進的過渡,讓正片鋪銅上的圓角或全圓角變得平滑。如果我們使用 GDSII 作為製造格式,這將導致產生許多非常小的片段 (並因此要求弧形是向量化的)。在這種情況下,我們可能會傾向於右邊的倒角形狀;它在輸出過程中不需要修改,即所見即所得。

上述解決辦法可以幫您省去幾個小時的繁瑣工作,快開啟你的 Allegro Package 工具進行嘗試吧!

更多 Allegro Package Designer Plus 操作技巧:

歡迎點擊下方圖片,瞭解更多 Allegro Package Designer Plus 指令功能!

若您正在使用 Allegro Package Designer Plus,並希望升級到 17.4 最新版本,

維護過期 用戶,請聯繫 映陽科技團隊

維護期內 用戶,請點擊下方圖片 ↓↓

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」