By Jason Yao, TopBrain China

作為代表未來趨勢的 SIP 技術目前正在軍民界如火如荼的開展進行中,這其中既有原單晶片封裝擴展為多晶片的量化增加,又有原 PCB 領域的的產品因對小型化需求而轉為尋找 SIP 方案的迫切需求。由於 SIP 整合涉及到較為複雜的系統,包括模組內部的細節、模組與外部的關係、信號的品質、延遲、分佈、雜訊等。電路與系統的設計水準成為評判是否具有 SIP 開發能力的一個關鍵指標。設計中要考慮的關鍵問題之一是載體上元器件的佈局和連線,這與 PCB 上的系統設計相似。另外還需要綜合考量載板上各晶片及元件在狹小空間內信號之間的串擾、雜訊、電通路的輻射等問題。

本次案例所要解決的問題就是在 SIP 載板上遇到的信號干擾問題。

基本資訊與問題

基本資訊

1. |

該產品由原來的 PCB 方案小型化而來,將原 PCB 中 IC 改為裸晶,減少被動元件使用 |

|---|---|

2. |

本次產品類型為 SIP 封裝,尺寸為 12x12mm,塑封類 |

3. |

基板為 4 層,晶片 (die) 排列方式為並排放置,共計 10 顆,其他被動元件共計 18 顆 |

4. |

信號為數模混合類 |

問題描述

SIP 載板在進行類比信號測試時,發現兩個類比信號上存在 15MHz 的耦合干擾,雜訊級別在幾十 mV,已經影響到電路的正常工作。

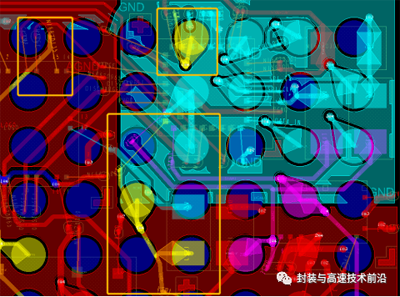

透過電路的分析以及 SIP 基板設計的排查,存在一路幅值為 5V、主頻為 15MHz 的時鐘信號,與出現問題的兩個類比信號處於同一區域,如下圖所示,右上角為時鐘信號,下面的類比信號 1,左上角的為類比信號 2。

基板設計方面,時鐘與類比信號走線同層的隔離地銅皮處理不當,存在孤島與碎銅,時鐘與類比信號各自線路並沒有被包地保護地很好,而且回流平面的處理也有問題;另外電路設計方面,針對主要的電源沒有去耦電容設計,加之平面設計不當,極有可能形成時鐘與類比信號的回流路徑耦合,因此懷疑是 15MHz 的時鐘信號與類比信號之間的平面耦合導致了串擾。

模擬思路

為了確定時鐘信號對類比信號的串擾大小以及找到耦合路徑並驗證優化方向,主要透過以下幾個步驟實現:

1. |

將 SIP 設計檔導入到 Cadence Clarity 3D Solver 模擬軟體中,進行 3D 全波電磁場模擬,將時鐘信號、類比信號以及相關網路的電磁耦合關係一併提取出來,得到精確的 S 參數模型。 |

|---|---|

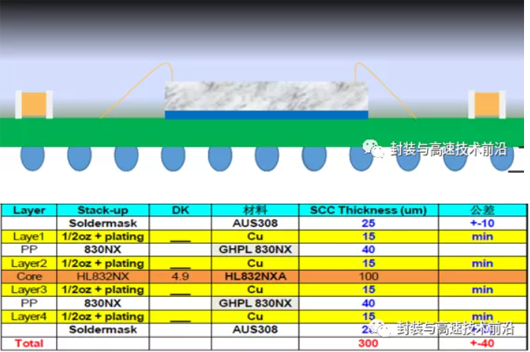

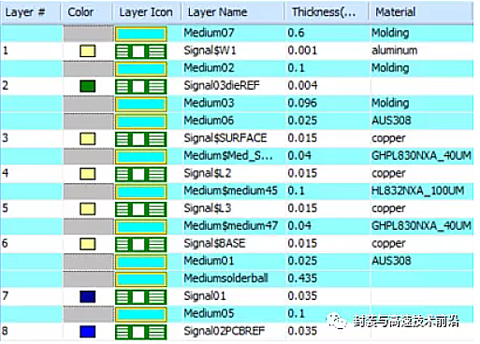

a ) 層疊設置,結構是包含從 Die Pad 經過 Wirebond、封裝基板、Solderball 到 PCB 的整個封裝路徑。 |

層疊結構視圖

b ) 埠設置,添加 lumped port 如下圖,Die 一側的 port+ 在 Die pad 上,port- 在新增 REF 層上,透過 DGND 短接 port 實現統一回流,BGA 一側的 port+ 在 BGA pad 上,port- 在 PCB 的 REF 層上,透過過孔延伸實現統一回流。 |

Die 與 BGA 側埠視圖

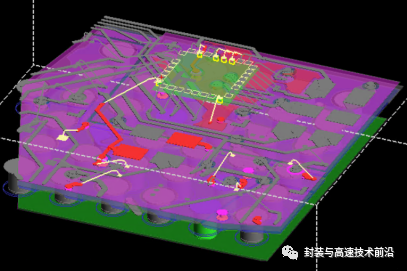

c ) SIP 的 3D 模擬視圖如下,在設置為層疊、埠以及模擬相關設置後,進行 3D 全波電磁場模擬。 |

SIP 模擬 3D 建模視圖

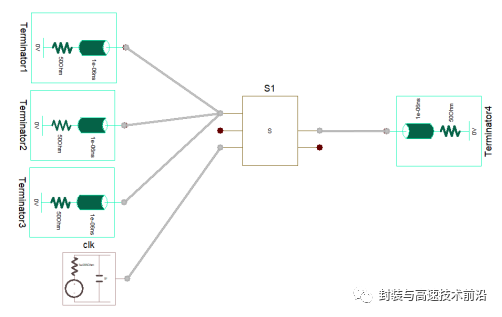

2. |

到 Cadence Sigrity Topology Explorer 中 搭建時域模擬連接,如下圖,包括時鐘激勵源 CLK (頻率為 15MHz,幅度為 5V),然後調入 Clarity 3D Solver 中提取的 S 參數,將激勵源 CLK 的輸出端接入 S 參數中時鐘的輸入埠,輸出埠接一個觀察 Prob,將類比頻道輸出端進行 50 歐姆端接匹配,透過輸入端的 Prob 觀察後向串擾時域波形和頻域頻譜。 |

|---|

3. |

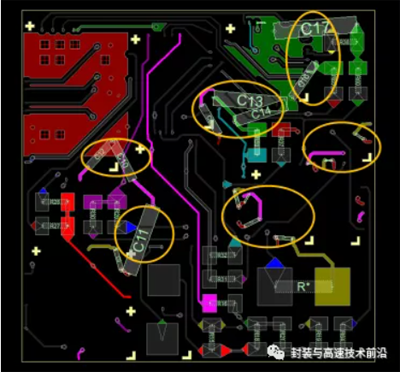

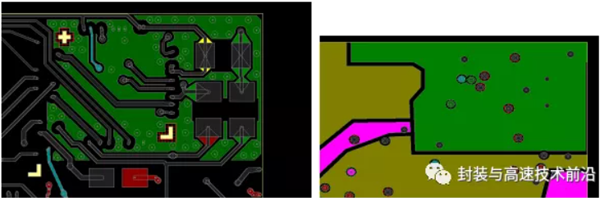

對設計進行 調整優化,驗證優化效果。採用兩種方案,一種是增加電源的去耦電容,如下圖,對主要的幾個電源增加 104 (0402 的 0.1uf) 電容,這裡除了模型提取的時候一起進行電源的 PDN 阻抗分析,驗證去耦電容效果;一種是修改優化版圖設計,包括地銅重新處理,去掉孤島,打上地孔,平面層銅皮間距拉大等。反覆運算模擬,驗證優化措施的效果。 |

|---|

增加電源去耦電容視圖

版圖優化視圖

模擬結果分析與改善

1. 原始設計分析

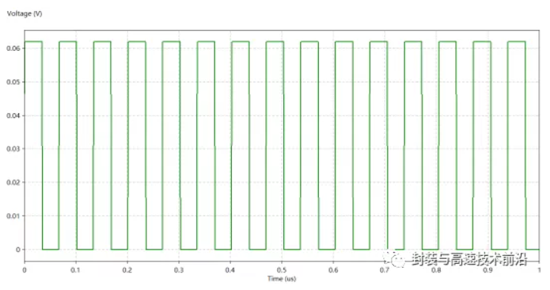

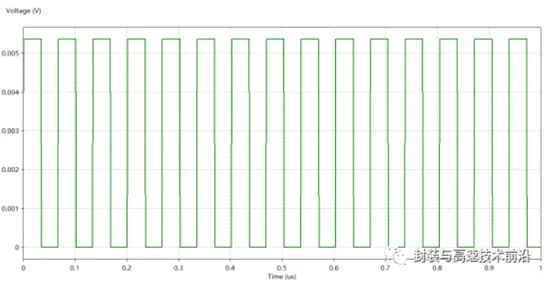

類比信號 1 的後向串擾時域波形如下圖所示,與類比信號 1 的串擾量為 62mV 左右,這個量級還是很可觀的,與測試結果相符,需要進行設計優化。

類比信號 1 的後向串擾時域波形

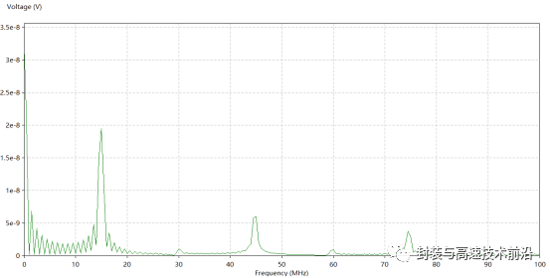

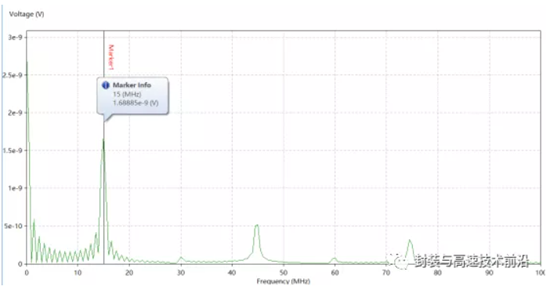

類比信號 1 的後向串擾頻譜如下圖所示,從頻譜上看,很明顯串擾的主頻在 15MHz 處,說明給予時鐘激勵後,透過耦合路徑,確實時鐘信號的雜訊傳導到類比信號 1 上去了。

類比信號 1 的後向串擾頻譜圖

類比信號 2 的後向串擾時域波形如下圖所示,幅度較小,因為空間上該信號與時鐘信號距離較遠,隔離相對類比信號 1 要好。

類比信號 2 的後向串擾時域波形

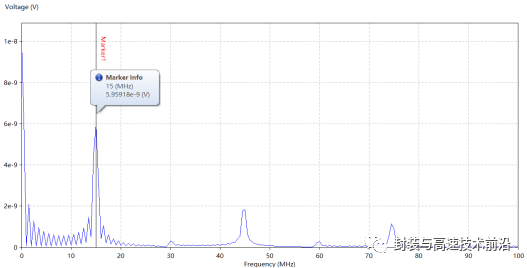

類比信號 2 的後向串擾頻譜如下圖所示,雖然時域串擾幅度較小,但可以透過頻譜圖看出串擾的主頻也在 15MHz,說明仍有時鐘信號雜訊耦合到類比信號 2 上。

類比信號 2 的後向串擾頻譜圖

2. 改善方案——增加去耦電容

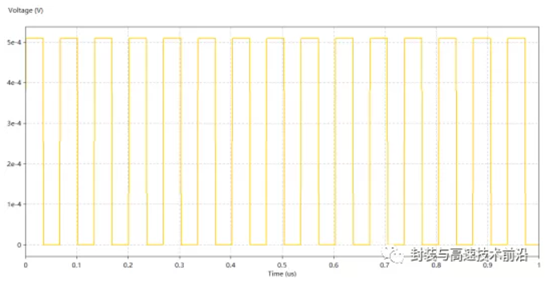

增加了去耦電容後,重新模擬,類比信號 1 的後向串擾時域波形如下圖所示,可見類比信號 1 的串擾量由 62mV 降到了 5.2mV。

增加去耦電容的類比信號 1 後向串擾時域波形

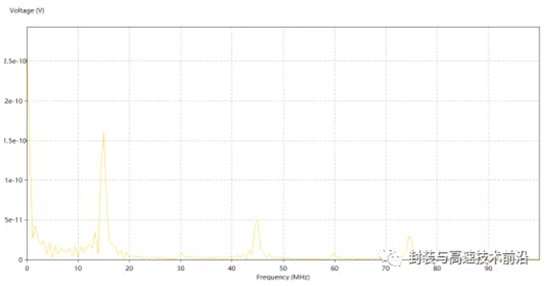

增加去耦電容後的類比信號 1 後向串擾頻譜如下圖所示,與沒加電容之前相比,下降了一個數量級,換算成 dB 值,大概下降了 20dB 左右。

增加去耦電容的類比信號 1 後向串擾頻譜圖

下圖為主要電源平面沒加電容與加電容後的 PDN 平面阻抗,在 100MHz 處,加了電容的 PDN 阻抗基本都在 0.15 歐以下,而沒加電容的 PDN 阻抗則大很多,基本在幾十歐,最大到了 300 歐,PDN 阻抗代表了電源平面的雜訊情況,可以非常明顯地看到加電容與否對電源平面雜訊的影響。

電源 PDN 阻抗曲線

3. 改善方案——版圖優化

版圖優化後,重新模擬,類比信號 1 的後向串擾時域波形如下圖所示,可見類比信號 1 的串擾量由 62mV 降到了 19mV。

版圖優化的類比信號 1 後向串擾時域波形

增加去耦電容後的類比信號 1 後向串擾頻譜如下圖所示,與設計沒優化之前相比,下降了一個數量級,換算成 dB 值,大概下降了 10.5dB 左右。本次只做了初步優化,後續如果有更全面的改善設計的話,預計可以得到更好的結果。

版圖優化的類比信號 1 後向串擾頻譜圖

針對兩種改善措施,考慮到本案例是 SIP 類產品方案,增加電容的解決辦法不可避免會擴大產品尺寸,這與 SIP 小型化的特性背道而馳。所以,建議優先選用優化設計的辦法來降低干擾提高性能。

案例結論

本次案例利用 Cadence 的 Clarity 3D Solver 與 Topology Explorer 對故障 SIP 基板進行了類比信號的干擾模擬,成功地對測試中的故障實施了複現及定位,並給出了兩種具體的改善措施,本次案例體現出了模擬在研發過程中的重要意義,減少了基板改板次數,縮短了產品研發週期,降低了研發成本。

歡迎點擊下方圖片,瞭解更多 Clarity 3D Solver 功能!

歡迎點擊下方圖片,瞭解更多 Allegro Package Designer Plus 指令功能!

本文授權轉載出處

封裝與高速技術前沿

微信號:APDtech