By Tyler Lockman, Cadence

BGA 元件的主要作用是將其保護的裸晶 (die) 的信號經由 BGA 的焊球重新分配到其所安裝的主機 PCB 上。因此,許多 IC 封裝設計團隊都不繪製前端電路圖。即使有電路圖,我們也可能在 layout 中直接交換邏輯信號,而佈線路徑的附加情況便是決策的關鍵。

與許多 ECAD layout 工具不同,Allegro® Package Designer Plus 工具提供了完整的邏輯編輯功能。我們可以創建並刪除 nets、指定給單個引腳,或者從一個元件介面傳輸至另一個元件介面。這種靈活性是封裝的核心本質,用來重新分配並保護較小的裸晶基板 (die)。

本文將討論一些常見情況:無論我們在中介層載板 (interposer) 上做覆晶封裝 (flip-chip)、在 BGA 上堆疊一組記憶體晶片,還是在系統封裝中的完整裝置陣列,這些情況均適用。

從 Die 到 BGA 或從 BGA 到 Die 的對應關係

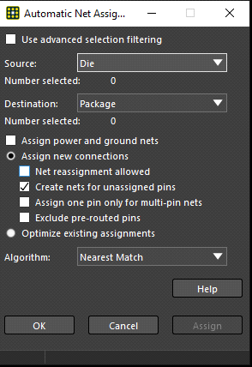

Logic - Auto Assign Net 功能已包含在 Allegro Packaging 工具多年。大家可能對此也十分了解,但要完整探討封裝連接性就不能不提到它。

如果我們準備啟動一個新的封裝設計,seed netlist (種子網表) 通常源於要封裝的 die。一旦將它們載入 layout 之後,就會生成一個合適大小及引腳數的 BGA。然後,我們需要將信號由 die 傳遞到 ball (焊球)。 除非已經預先定義好 BGA 的網表,否則使用 Auto Assign (自動分配) 功能是最好的方式。

有兩種演算法來執行分配。Nearest match (最近點匹配) 會嘗試將所有連接點的鼠線總長度最小化,同時最大限度減少鼠線交叉。 而依據約束設定分配則將著眼於傳輸延遲、差動對成員關係以及類似因素的詳細要求,並儘量滿足此類條件。

當我們選擇了適當的演算法並確定了一些基本要求 (像是對來源中未分配的引腳創建 nets,以及是否將任何現有的 BGA 焊球分配視為不可變) 時,選擇「至/自」元件 (或引腳組) 並按下「assign (分配)」按鈕,將為封裝的網路匹配獲得一個合理的配置。

但在這樣做之前,我們必須導入所有晶片元件,以便工具根據情況資訊做出明智的決定。如果我們有一組堆疊的晶片,在封裝內部具有共用信號,那麼一定不希望 BGA 球被分配用於共用信號!

基於佈線設計規則檢查 (DRC) 的連接性

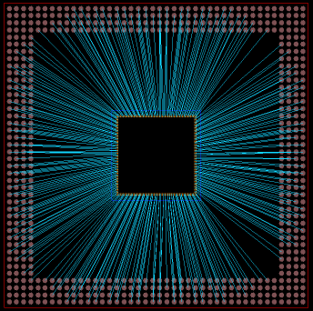

如果我們不選用自動分配功能,則需要先開始佈線並觀察走勢。 當看見滿意的結果時,便可以指定分配給 BGA。

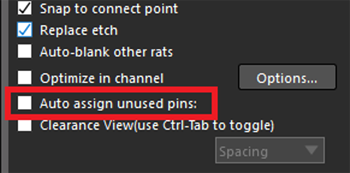

首先,利用互動式佈線工具內建的分配功能。 如下圖所示,如果要將未使用的引腳分配給 BGA,需打開自動分配未使用的引腳選項。 到達目標點並點擊時,BGA 焊球將被分配到晶片引腳的 net 上來完成連接。

這是一個非常實用且省事的做法。但當使用這樣的方式做分配,就意味著我們已經鎖定了該 BGA 焊球,之後佈線器中的自動分配選項便無法再改變它。 如果需要重新對應引腳,則需要手動取消分配 (或使用 swap 交換功能)。

為了使選擇完全開放,我們可以不選擇自動分配未使用的引腳功能。 如此一來便不會指定 BGA 焊球,並且在佈線末端和引腳之間會顯示 DRC 衝突。 不過不需要在意這個標記,它可以驅動另一個邏輯選單指令 —— Derive Assignment,待準備要指定分配時便可使用。

如上所示,Stretch traces (擴大走線) 功能選項是重點。 打開此功能後,如果先前的佈線在焊球的 pad 上,但沒有精確的連接好時,Derive Assignment (獲得指定) 功能便會自動調整連接。這樣可以確保接點的圓角鋪銅乾淨漂亮。

Derive Assignment 功能的第二個目的是,它可以使用 DRC 解析並指定給其他物件 (vias、shapes、bond fingers),而不僅僅是引腳。使用此功能,系統可以評估佈線和鋪銅,並根據它們綁定的物件將電壓 nets 分配到平面鋪銅區域。

在設備之間推送所選連接

最後,當對一個元件 (通常是晶片) 進行 ECO 工程變更並需要將其導入 BGA 時,會發生什麼呢? 17.4 QIR1 版本 (hotfix 007) 引進了新的邏輯管理功能:Push Connectivity (推送連接)。啟用此功能前,請在使用者設定選項中啟用 icp_push_connectivity 功能,然後重新啟動軟體:

之後,我們將在 Logic (邏輯) 功能表中找到新指令功能,以及其他指令功能 (在 Derive Assignment 下方)。此功能專門設計來將更新後的 nets 導入與所選擇的元件引腳共享實體連接的專案。

它與 Derive Assignment 功能不同,後者僅基於 DRC 來解決與 dummy net (虛擬網路) 物件的連接。 而該推送功能並不基於 DRC 違規檢查,僅經由 layout 本身的實體佈線路徑推送。因此,介面的選項非常簡單——只有一個選項!如下所示:

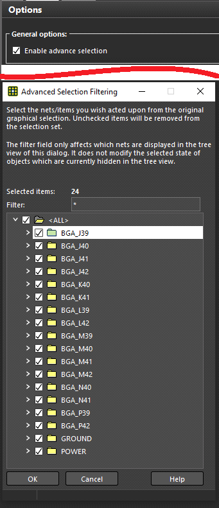

在選擇要從中推入連接的一組引腳之後,當進階選項打開時,我們將看到一個列出所有 nets 及其引腳的表格,可以從中進行篩選。 無論是僅推送信號網路,或僅推送這些網路上特定引腳的網路,我們都可以在此自訂選擇 (小提醒:我們將在 auto-assign net 功能中看到相同的介面)。 這與一般搜尋介面並不衝突,兩種都可以自由使用。 對於一次性操作,進階選擇篩選器可以更快地集中顯示所選資料的樹狀圖。 但是,如果已經保存了查詢結果用於其他用途,則可取用其中一種。簡而言之,最有效的方法就是最好的方法。

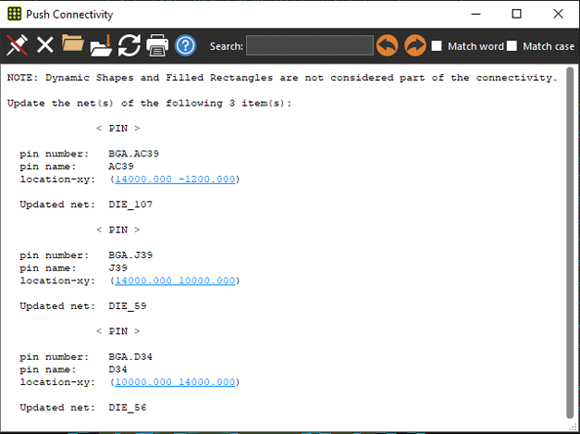

當有了要傳輸的項目之後 ,就可以開始進行作業。 資料庫將找到這類 nets 的連線關係,並更新其遇到的任何引腳、過孔和形狀的分配。 與上方的 derive assignment 功能不同,push connectivity 功能會對目前已有不同 nets 的元素做重新分配,而不僅僅是 dummy nets 物件。

分配更改完成後,會顯示一份報告,列示所有已更改的內容,以便我們進行確認:

總結

短短一文無法涵蓋所有內容,本文尚未具體談到協同設計晶片元件以及流程。 對於任何協同設計的晶片元件 (從而瞭解晶片中的第一層單元結構,以便能夠針對晶片內部 I/O 宏觀佈局的影響來驗證建議的封裝分配更改),Allegro Package Designer Plus 將防止我們對 IC layout 進行無效編輯。這將在優化凸點模式時,説明使用者最大限度地減少與晶片設計團隊的來回溝通。

在「 File-Import 」和 「 Logic 」功能表中查看許多其他命令功能,以及「 Symbol Edit (符號編輯)」應用模式,即可找到滿足您特定需求的最佳解決方案。

歡迎點擊下方圖片,瞭解更多 Allegro Package Designer Plus 指令功能!

作者簡介

Tyler Lockman

Cadence Software Architect

於加拿大卡爾頓大學獲電腦科學學士學位後,在 Cadence Allegro 產品部門工作超過 20 年,專注於 IC 封裝與中介層基板設計。 同時,參與全 Allegro 平臺、Virtuoso、PVS、OrbitIO 及 Innovus 產品的核心工作。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」