很多年前大家就認為 3D 封裝的時代很快就會到來。

但是,3D 封裝就像砷化鎵 (Gallium Arsenide) 一樣,總是「即將」要衝進主流,卻從未進入主流。全球半導體聯盟 (GSA) 已經對此失去了耐心。事實上,3D 封裝是一種需要面面俱到的技術轉變,如同在製造業發生的從 8 寸到 12 寸晶圓的轉變。所有涉及的個體都必須前進,否則無法真正實現 3D 封裝。就封裝而言,不僅需要有可用的技術,而且還需要設計工具、製造商來做好批量生產準備且能夠保持較低的成本。

走向主流

相較於仍將所有專案全部集成到單個系統級晶片 (SoC) 上的傳統方式而言,3D 方法有以下幾個潛在優勢:

在人們認為摩爾定律正在消退的情況下,透過「超越摩爾」一詞廣為人知 |

|

無需在最先進的節點上構建出整個晶片,只需要構建可以利用的部分 |

|

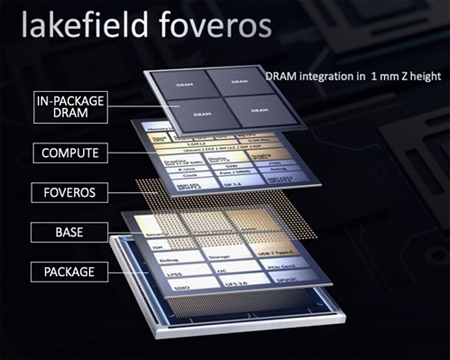

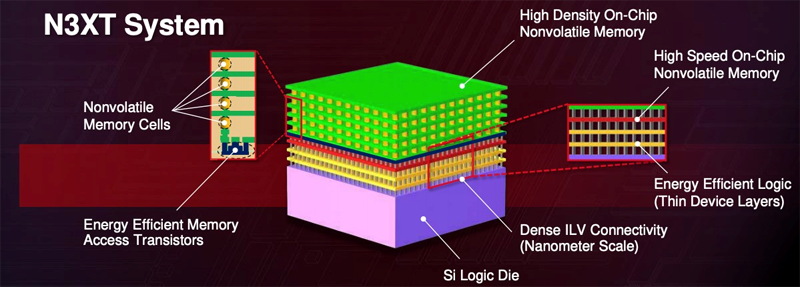

可將與基本邏輯制程 (如 DRAM 或 RF) 不相容的制程混合到設計裸晶中 |

|

在鰭式場效電晶體 (FinFET) 時代,模擬和 RF 都很困難甚至不可能,並且在等比例縮小的工藝制程中得不到任何面積縮小好處,因此對於具有大型模擬器件的設計而言,系統級晶片方法並不適用 |

|

由一整塊巨大晶片構建而成的指定矽面積,其良率會比利用 3D 封裝拼接在一起的多塊獨立裸晶所形成的相同矽面積的良率低很多 |

但其缺點基本上也具有如子彈般的殺傷力:

過於昂貴 |

目前面臨的挑戰是一種類似於先有雞還是先有蛋的問題:因為只有當 3D 封裝比單片整合或其他可選方法 (如層疊封裝 (package-on-package,PoP)) 更便宜時,才會用於大批量生產。但是,只有在大批量生產時,3D 封裝才會變得便宜。當然,半導體晶圓製造也面臨這個問題。目前,一塊 5nm 晶圓預計價值數百萬美元,如果所有的 5nm 晶圓都要花費數百萬美元,那麼沒人會購買。但所有人都知道,一旦解決了初期困難,並且每個月能夠生產出數以萬計的晶圓,那麼成本自然就會下降。事實上,整個半導體行業都依賴於這條軌跡的真實性。

在去年夏天的 HOTCHIPS 大會上,很多被冠以熱門的「晶片」實際上都是 3D 封裝系統。這樣看來 2019 年最終還是成為了新摩爾定律成真之年。

邁向主流之路的關鍵是一款很吸引人的被稱之為扇出型晶圓級封裝 (fanout wafer-level packaging,FOWLP) 的技術,以及行動產業對該技術的使用。行動產業是唯一一個擁有足夠交易量,因此能夠完全改變整個製造生態系統的行業。一旦行動產業提供了交易量,經濟狀況就會發生變化,而這種技術也就可以用於低交易量市場。此外,其他技術也開始得到應用。基於仲介層的各種方法也成為了主流方法。在一個資料包中放一片以上的裸晶,似乎也不再是冒險或愚蠢行為。

Chiplets

以下是 HOTCHIPS 大會上 AMD 演示的一個章節,它呼應了上文提到的很多要點:

用於組裝這些系統的裸晶通常被稱之為 chiplets,因為它們比晶片小,並且也並非是針對獨立使用而設計的。HOTCHIPS 大會上展示的所有設計中都包含有專門針對該設計製造的 chiplets。所採用的製造方法不是製造一整塊大型的單片系統級晶片,而是設計三到四塊 chiplets,然後利用先進的封裝技術將這些 chiplets 組合在一起。

那麼,半導體生態系統是否會轉向以 chiplets 為基礎? 在代替由單片系統級晶片或 PCB 上的獨立系統級晶片所組成的系統時,能否利用從不同的半導體製造商處購買到的chiplets組裝系統呢?事實上,Cadence 公司就生產出了這樣一款作為裸晶對裸晶 (D2D) 互連的測試 chiplet。關於這方面的資訊,可以參閱文章《 產業觀察|裸晶對裸晶互連:UltraLink D2D PHY IP 》。

很明顯,要做到這一點還需要解決一些技術問題和標準問題,但最大的問題可能是商業模式問題。對於超大批量的設計,沒有人有足夠的庫存來接下突然而來的一億個零件的大訂單。但對於較小的交易量,需要有人因為持有庫存並因此獲得相應的補償。這可能是半導體公司、智慧財產權公司、 傳統器件經銷商、甚至是專門為服務這類市場而成立的新公司。 時間會告訴我們答案。

線上研討會

針對上文所述問題,Cadence 公司高級半導體封裝產品管理團隊總監 John Park 線上上研討會「下一代異質整合 2.5/3D 積體電路設計的設計方法學」中給予了進一步的闡明與介紹,並帶來了最新的高級 Multi-Chip(let) 封裝解決方案,包括確定最適合您設計類型的 layout 工具流程、高級 Multi-Chip(let) 積體電路封裝的頂級設計聚合與管理測試和驗證,以及跨領域的電熱建模。

| 視頻 節點 | 研討會內容 |

|---|---|

00 : 10 |

先進 IC 封裝趨勢Top Trends for Advanced IC Packaging |

02 : 09 |

開啟超越摩爾時代The Beginning of the “More Than Moore” Era |

03 : 21 |

摩爾定律走向終結了嗎?The End of Moore’s Law…Really? |

05 : 40 |

超越摩爾時代的挑戰Transitioning to More Than Moore…The Disaggregated SoC |

07 : 07 |

如何讓 chiplets 成為業界設計主流Final Hurdles for Chiplets to Move into Mainstream Design |

08 : 57 |

Multi-Chip(let) 封裝技術演進Evolution of Advanced Multi-Chip(let) Packaging Technologies |

10 : 56 |

下一代異質整合 2.5/3D IC 設計工具 / 流程挑戰Design Tool/Flow Challenges for Next-Gen Heterogeneously Integrated 2.5-IC and 3D-IC Designs |

12 : 51 |

Multi-Chip(let) 先進封裝設計解決方案Solutions for Multi-Chip(let) Advanced Package Design |

13 : 46 |

Virtuoso 智慧系統設計平台Virtuoso Intelligent System Design Platform |

14 : 26 |

Virtuoso Multi-Chip(let) 智慧系統設計平台Virtuoso Platform for Multi-Chip(let) Intelligent System Design |

17 : 16 |

針對 Multi-Chip(let) 設計的 Allegro Package Designer Plus 技術方案Allegro Package Designer Plus for Multi-Chip(let) Design |

18 : 39 |

Allegro Package Designer + Silicon Layout Option |

19 : 40 |

Cadence 電熱建模技術Cadence Technologies for Electrical / Thermal Modeling |

20 : 48 |

Multi-Chip(let) 設計流程Multi-Chip(let) Design Flow |

23 : 18 |

Cadence Multi-Chip(let) 封裝跨平台解決方案Cadence Cross-Platform Solutions for Multi-Chip(let) Packaging |

24 : 07 |

精選問答 |

內文搶先看:

該視頻 (簡體中文字幕) 全長 30min,歡迎填寫下方索取表,索取 完整研討會視頻和 PPT 講義。

講師介紹

John Park,Cadence 高級半導體封裝管理總監,35 年從業經驗,Cadence RF SiP 產品線初始架構師,專注於跨晶片 - 封裝 - 電路板多領域、系統級別設計和優化解決方案。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」