《SiP 前世今生》系列文章由 Cadence 專欄作者 Paul McLellan 撰寫。該系列共三篇文章,第一篇《為何系統級封裝是大勢所趨?》與第二篇《系統級封裝因何驅動?》聚焦於 SiP 的驅動因素與技術發展,本篇文章的重點是如何著手進行系統級封裝設計,將討論的部分內容甚至適用於更簡單的設計,即單個晶片的單一封裝,尤其是採用複雜的封裝技術時。

首先,如上圖所示,封裝設計有許多處理方法:

採用以機構引線框設計封裝本身 |

|

採用可佈線的有機和陶瓷基板設計封裝,這是一種 PCB 形式的設計流程 |

|

設計 2.5D 矽中介層、嵌入式橋和扇出型晶圓級封裝(FOWLP)的混合設計流程 |

|

採用積體電路類設計流程設計具有矽穿孔(通常)的 3D 積體電路 |

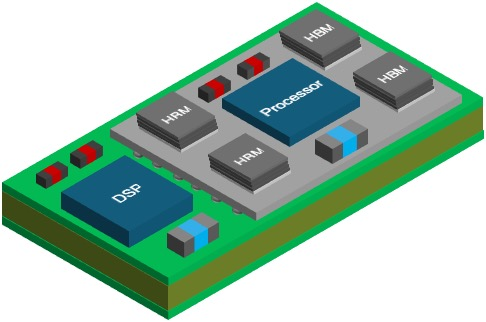

下一代封裝的異質性可能更高,例如,將 3D 堆疊放在 2.5D 矽中介層上,如上圖所示,而 2.5D 矽中介層又放在具有更多器件的有機中介層上。

這種類型的設計會面臨許多挑戰:

頂級設計聚合和管理 |

|

- 預佈局規劃 | |

- 頂層(晶片到晶片到封裝到 PCB)網表定義 | |

- 系統級 I/O 優化 | |

理解晶片(chiplet)提取 / 表示的正確層級 |

|

- 簡單(範圍和引腳位置) | |

- 複雜(全晶片(chiplet)) | |

先進的多晶片(chiplet)積體電路封裝需要專門的驗證 |

|

- 由頂層管理工具驅動的佈局與電路圖(LVS)連接驗證 | |

- 高級晶片間對準檢查 | |

- 矽基底設計和驗證方法 | |

跨域電 / 熱建模 |

|

- 模擬域間的耦合效應? | |

- 為積體電路、封裝和 PCB 連接不同的提取工具 |

實現和簽核

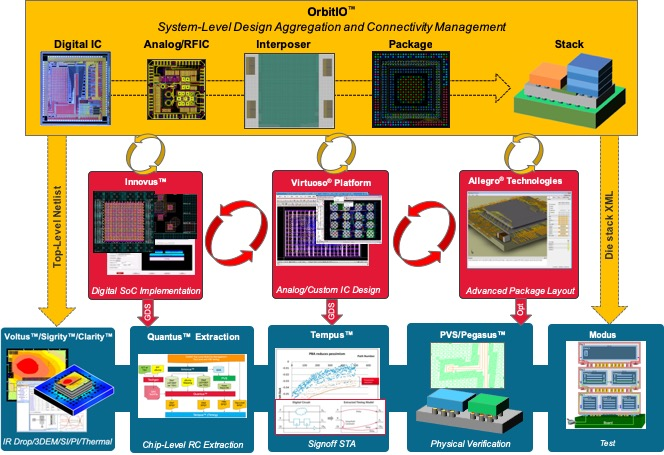

Cadence OrbitIO™ 軟體是為規劃、優化和管理設計專門打造的工具,用以處理頂級電路圖、網表以及所有晶片堆疊。

再透過 Cadence 的實現工具組合來具體實現:Innovus™、Virtuoso® 以及 Allegro®。此外,還有一套提取、驗證和簽核工具:Voltus™、Sigrity™、Clarity™、Celsius™ 等軟體。

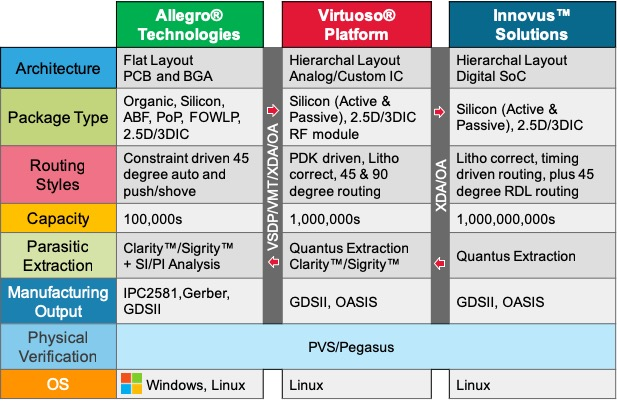

哪種實現和驗證平臺最合適取決於設計風格,即在很大程度上取決於是否類似 PCB 設計(在這種情況下,Allegro 和 Sigrity 等工具是最佳選擇),或者是否類似積體電路設計(在這種情況下,Innovus 和Voltus 等工具是最佳選擇)。上表深入說明了所涉及權衡的更多細節。

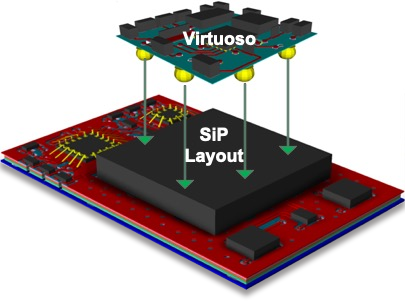

所有的多晶片工具都可以處理多個 PDK,因為晶片通常採用不同的技術,但需要一起分析。例如,也可以透過 SiP 的 context 打開 Virtuoso 的 IC 設計來檢查(或更改)晶片。資料庫是共用的,因此不必一直從一個工具中寫出檔,然後再將它們讀回到另一個工具中。雖然每個工具都有獨特的功能,但它們都有跨平臺的功能。

透過本文無法介紹完所有工具的功能,尤其是在工具涵蓋範圍極其廣泛的情況下,即包括機構建模、PCB 設計、積體電路設計、晶片級信號完整性、板級和封裝級信號完整性、熱電建模、射頻、矽光子學......事實上,幾乎涵蓋了 Cadence 的所有 EDA 技術。

分解式系統級晶片

系統級封裝(SiP)正在成為新的系統級晶片(SoC)。這是因為它們都是集成方法,但更重要的是,系統級封裝最具成本效益,且最高效。根據定義,在系統級晶片中,一切都必須採用同一制程。自晶片尺寸足以容納微處理器和所有支援邏輯以來,這一直都是主要的集成方法。但現在,並非每個邏輯功能都需要採用同一制程。還有一些標準化 chiplet 介面的舉措,藉此,使用系統級封裝方法來構建分解式系統級晶片將變得更加簡單。

Cadence 與合作夥伴在3D積體電路方面的合作已有十多年,已經完成了 10 多項測試設計,包括多項生產流片和系統級封裝設計;更多項目仍在進行中,歡迎大家持續關注。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」