隨著技術的發展,封裝設計變得越來越複雜。新材料和製造工藝的出現,使得封裝中可以有更多有源和無源元件。

與此同時,信號完整性、電源完整性和熱挑戰也隨之增加。以前可以在機械 CAD 工具中完成的簡單設計,現在需要接受更為嚴格的設計規則檢查。運行信號完整性(SI)分析和製造檢查也勢在必行。那麼,如何順利完成複雜封裝設計的各個階段呢?

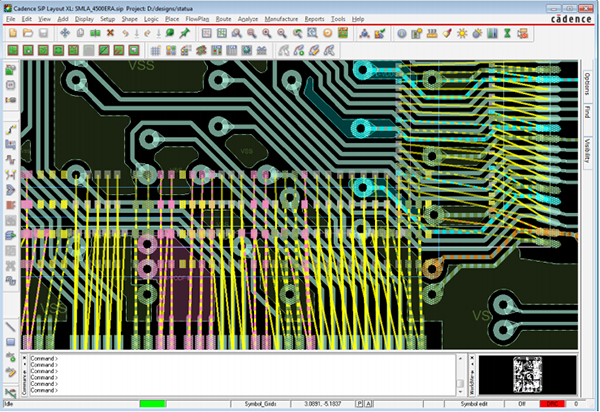

Allegro® SiP Layout 工具,憑藉大量命令和工具集可以幫助我們更快速地完成封裝設計,並透過各級驗證保障最終元件能在整個系統環境中完美運行。

來源:SiP Layout 工具

從技術上看,不僅與其自身晶片強大的資料處理有關,也與其優越的 MIC 性能有關。

※ 據分析其耳機內部用到的 MIC 全部來自於歌爾股份。而這些正是通過使用 SiP(系統級封裝)技術來實現。

第一步:從外部幾何資料預置基板和元件

任何設計中,第一步都是準備好元件。如果我們有器件庫和器件檔,便可以開始設計了。但是,如果我們只有一個晶片 GDSII 檔和簡單的網路文本標籤,或者晶片焊盤圖案的試算表引腳圖,甚至只有一個來自基板供應商的定義的引腳圖案、焊盤的 DXF 檔,要怎麼辦?

無論我們的來源是晶片文字檔、協同設計晶片摘要還是製造幾何資料,SiP Layout 都能滿足導入和轉換需求。輕鬆幾個命令便可以將資料轉換為基板中完全定義的元件和符號;基板有網路指派,並做好了接合準備。此外,我們可以直接在 SiP 基板設計中完成這些工作,無需進入庫元件或焊盤形狀編輯器。因為在編輯器中,我們將失去整個封裝的環境(重建智慧基板期間的重要資訊,包括幾何資料)。

以下是一個簡單的圖表來瞭解選項細節:

更多的特定資料登錄清單可透過點擊:檔 -> 導入和添加 -> 標準晶片功能表項目來查看,或諮詢 Graser 技術團隊。

如果對於某個設置使用了不同數量記憶體或不同電源的設計,我們有多種不同的選擇並且想確保一次性輸入所有資料,怎麼做呢?不用擔心,SiP Layout 可以幫助我們發現各個不同的組合,並從主基板設計中提取單獨的資料庫用於驗證、分析和製造。

第二步:將元件連接至封裝引腳

我們將元件放置好並準備進行連接後,一切就變得簡單了。但是,我們要確保在連接前完成閱讀網表資訊,從而確定要將哪個晶片焊盤連接到哪個封裝的引腳上。

從試算表、CSV 檔、電路圖或其他來源導入網路,或者根據引腳名稱/編號以及晶片到封裝引腳的優化分配即時定義網路。選擇我們最容易獲取的資訊,這一步將顯示晶片和引腳之間的連接線,此時我們便可以開始進行連線了。

第三步:執行物理 / 元件設計驗證

連線結束後,接下來應該驗證設計的物理特性。現在開始對設計進行3D檢查以確認設計情況(並且進行3D線至線DRC間距檢查);點擊 View -> 3D Model,定義 DRC 需求,並生成視圖。如果我們發現任何問題,可以直接在檢視器中更改引腳剖面,重新進行 DRC 檢查,並在情況完全符合我們要求時將新分佈分配回 layout 資料庫。

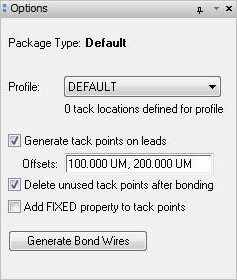

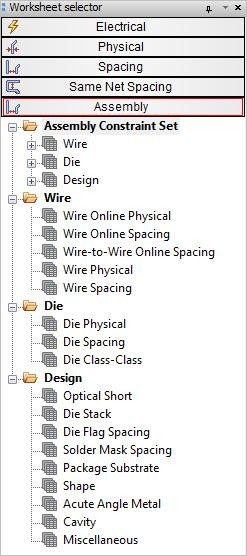

與 3D 檢查同樣重要的是,除了 Constraint Manager 試算表中的標準物理、間距和電氣規則之外,SiP Layout 還提供了強大的組裝規則檢查。下圖所示為組裝規則檢查類別:

如果我們的製造過程需要特定的專有規則,Cadence RAVEL option 可以確定在設計上運行特定的規則檢查。

第四步:電氣特性分析

電氣特性分析可以確保一切設計都在規格範圍內。

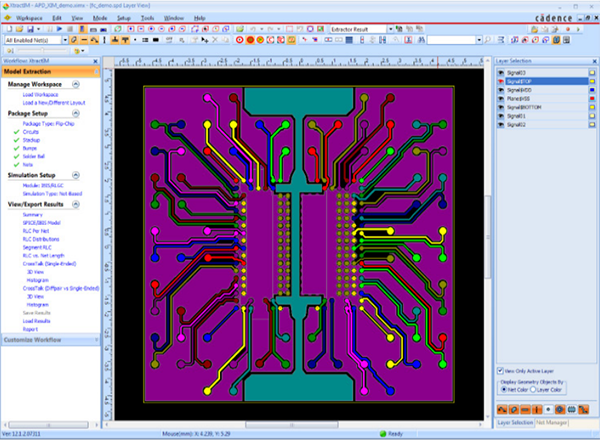

Sigrity™ XtractIM™ 工具是一個快速高性能的用於 IC 封裝 RLC 檢查和評估的工具。借助生成高精度寬頻模型並支援複雜封裝的功能,它適用於緊密整合的 SiP Layout 設計。Sigrity XtractIM 工具無縫地從設計中提取所有細節——3D 引線側視線型、焊料凸塊模型,甚至是開腔或者疊層晶片中晶片的位置和高度。

來源:Sigrity XtractIM 工具

第五步:生成製造資料和支援文檔

在創建設計、添加邏輯、驗證滿足物理和間距要求、並確保信號、熱和功率容差都符合規範之後,我們需要生成設計文檔和製造資料。

無論我們的需求是否包括鍵合圖、OLP 資料、GDSII、DXF、Gerber 或其他資料格式,基本上都可以在 File -> Export 或 Manufacture 功能表下找到滿足需求的匯出轉換器。

對於檔而言,無論我們需要設計的引腳連接報告、連通性報告,還是 PDF 文檔,輸出都輕而易舉。如果我們需要突出顯示設計的某些特定區域,使用 3D 檢視器的標記和注釋功能即可,截取帶有文本符號的詳細圖像並納入參考範圍。

本文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」