《 SiP 前世今生 》系列文章由 Cadence 專欄作者 Paul McLellan 撰寫。該系列共三篇文章,前兩篇聚焦於 SiP 的驅動因素與技術發展,最後一篇內容重在闡明 SiP 的設計挑戰與解決方案。

本文是《 產業觀察 | SiP 的前世今生(一):為何系統級封裝是大勢所趨?》一文的延續。本文著眼於促使系統裝配越來越多地採用 3D 封裝技術,而非將一切都整合到一個巨大的系統級晶片上的若干驅動因素。

異質性 ( Heterogeneity )

採用分離晶片的一個動機不僅僅是在單個製程中分割設計,而是封裝來自不同製程的晶片。

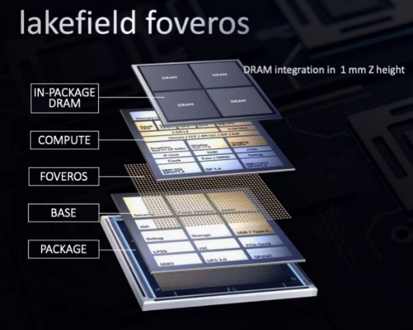

另一動機來自經濟方面。HOT CHIPS 大會上的演講將設計分割成處理器本身和設計的 I/O 部分。處理器可以採用最先進、最昂貴的節點製造,而 I/O 則可以採用不夠先進、較便宜的節點製造(通常落後一代)。下方圖片是 Intel 的 Lakefield 晶片,它有一個 I/O 基片(採用非前瞻的 14 奈米製程),10 奈米製程的處理器,以及封裝在頂部的動態隨機存取記憶體(DRAM)。這些都採用 Intel 的 Foveros 3D 技術組裝。

這樣做有兩方面的原因。最顯而易見的原因是,採用更先進的節點無法提高 I/O 介面的性能。當今,電晶體的先進節點更加昂貴,所以受經濟因素的限制而不能大力推廣先進節點的發展。但還有一個更微妙的原因。在生產中或者至少在測試晶片中,所有的 I/O(和其他常規模組)都已經整合到矽片中。如果 I/O 晶片也採用最先進的製程技術生產,那麼高速 SerDes 等的測試晶片就會構成退出整個系統的關鍵路徑。

採用先進節點時,射頻 (RF) 和模擬獲益更少。事實上,不僅不會受益,還將成為不利因素。採用鰭式場效應電晶體(FinFET)的製程來設計類比電路非常困難,因為 FinFET 是量子化的。電晶體的長度是統一固定的,而寬度是鰭的整數倍。在平面製程中,類比電路設計人員可以選擇電晶體的寬度和長度。模擬設計中,最重要的通常是關鍵電晶體之間的尺寸比。但是在 FinFET 中,兩個電晶體的尺寸比不能為任意數值,所以需要進行類比設計。繼續採用 28 奈米等平面製程,甚至是 65 奈米等較為不成熟的節點進行模擬設計更為合理,因為採用這樣的製程工藝進行設計(比如:模數轉換器)已經實現了很好的例化以及大規模生產。

雖然我不是射頻方面的專家,但我知道,幾乎不可能採用 FinFET 製程來設計射頻,因為 FinFET 電晶體本身具有高電容。對於射頻,互連的高電阻也能成為一個問題。

另一方面,採用單獨的晶片對一些光電器件來講是具有吸引力的。儘管核心晶片上會佈置一些光電元件,但不大可能佈置雷射器。通常,雷射器採用 InP(磷化銦)製造。在 2019 年美國舉辦的 Photonics Summit 上,Intel 的主題便是構建雙晶片解決方案,然後進行晶圓對晶圓的連接。

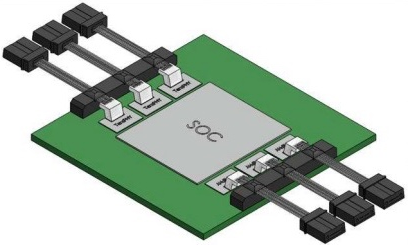

在 HOT CHIPS 大會上,Ayar Labs 介紹了其 TeraPhy 晶片,這是一種小型光學晶片,可以添加到系統級晶片封裝中,用以提供光學連接,如下圖所示:

Chiplets

目前,在討論多晶片封裝的 3D 設計時,都有個假設前提,即:這些晶片均由同一個團隊設計,或者至少由同一個公司設計;該假設不包含 DRAM,因為 DRAM 都來自專業的 DRAM 製造商。DRAM 必須大規模生產才會具有競爭力,而「大規模」指整廠一次產量。

但也存在另一種可能,那就是封裝內器件實現商業化銷售。此處的封裝內器件便是 Chiplets。其商業化銷售還面臨著若干挑戰。其中一些是技術上的挑戰,除此之外還有兩個挑戰——標準化和市場。事實上,Cadence 目前有一個專案正致力於解決其中一些問題。

如果同一個團隊正在設計的兩個晶片將放入同一個封裝中,他們幾乎可以選擇任意通信方案。但是,如果 chiplets 在某種意義上是標準的,例如,高速 SerDes chiplet 或 WiFi chiplet,那麼系統級晶片必須使用該 chiplet 提供的介面。為了使工作簡單化,介面最好經過驗證,且是標準介面。封裝內的各種距離都較短,因此不宜採用適合在底板上運行的同類型長距離 SerDes。另一個優勢是,相比透過封裝傳輸到電路板,在封裝內進行大量連接的成本相對較低(例如,寬版記憶體可以有數千個連接,而不用在八個或九個通道中傳輸所有資料)。

Cadence 於 2019 年底發佈了 UltraLink D2D PHY IP 產品,以及一款測試晶片(或測試chiplet),並對其進行了矽驗證。該測試 chiplet 採用了我們的 40Gbps SerDes,設計功耗非常低,並且能夠最大限度地提高 chiplet 邊緣(有時稱為海濱)的連線性,而由於間距非常小,並不需要採用昂貴的製程。

Chiplet 技術的支持者希望形成一個基於已知合格晶片(KGD)的 chiplets 市場,如此一來,便可以像在開放市場上購買 HBM 一樣,購買各種各樣的 chiplets。設計也會變得更像電路板級的系統設計:可購買標準器件,甚至可能將單個系統級晶片設計成系統的核心。

對此,我有一點懷疑,因為庫存問題似乎很難解決。當我在 VLSI Technology 工作時,我們總是遇到閘陣列基礎的庫存挑戰。閘陣列設計的好處是,所有的基礎都經過預擴散,然後保存在晶圓庫中。這對於小批量的簡單設計來說,效果很好。但有一個艱難的權衡。晶圓庫中的任何晶圓都代表著已佔用且正在貶值的金錢(而且,如果新的製程時代到來,還可能會過時)。另一方面,閘陣列的好處在於,晶圓庫隨時可用,因此可以相應縮短訂單的周轉時間(這段時間內,只需在存儲的晶圓上添加三層金屬即可)。如此,我們便不再需要具有不同記憶體門結構比的基礎晶圓。

Chiplets 的價值主張是:

可以靈活選擇零件的最佳製程節點——尤其是 SerDes I/O 和類比,不需要採用「核心」製程節點 |

|

由於晶片尺寸較小,良率更高 |

|

透過使用預先存在的 chiplets,縮短積體電路的設計週期和整合的複雜度 |

|

透過購買已知合格晶片(KGD),降低製造成本 |

|

在多個設計中使用相同的 chiplets 時,具有批量製造的成本優勢 |

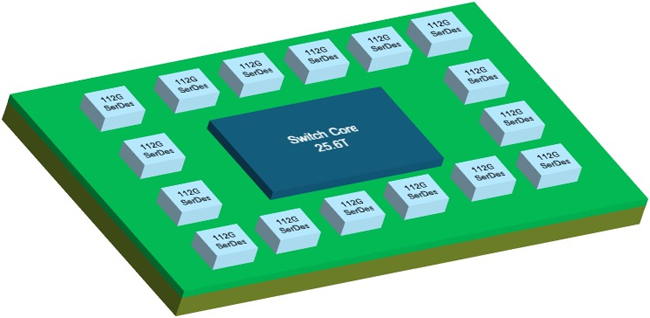

對於任何系統級封裝解決方案,前幾點都一樣。如果可以直接從經銷商那裡購買 chiplets,那麼後三點的效果是最好的,但如果特定的系統需要專門製造的 chiplets,也基本上將是這樣。優勢是,可以設計類似系統,如整合了 112G SerDes 的 25.6Tbps 轉換器,而不是把所有 SerDes 介面都整合到較大核心系統級晶片上。

本篇內容至此結束,下一篇文章中我們將聚焦於 SiP 的設計挑戰與解決方案,請大家繼續關注。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」