By Paul McLellan, Cadence

2022 年 3 月,第 18 屆國際設備封裝會議和展覽 (簡稱 IMAPS,是主辦方國際微電子組裝與封裝協會- International Microelectronics Assembly and Packaging Society 的首字母縮寫) 順利開幕。就在同一周,蘋果發佈了 M1 Ultra,使先進封裝再次成為了科技新聞的關注焦點。M1 Ultra 由兩個被仲介層 (或稱之為互連橋) 連接在一起的 M1 Max 晶片組成。仲介層通常比在其之上的裸片更大,而互連橋則較小,並只位於連接處的裸片邊緣之下。

在 此次 IMAPS 會議上,Cadence 資深半導體封裝管理總監 John Park 先生闡述了 3D 封裝與 3D 整合的區別。

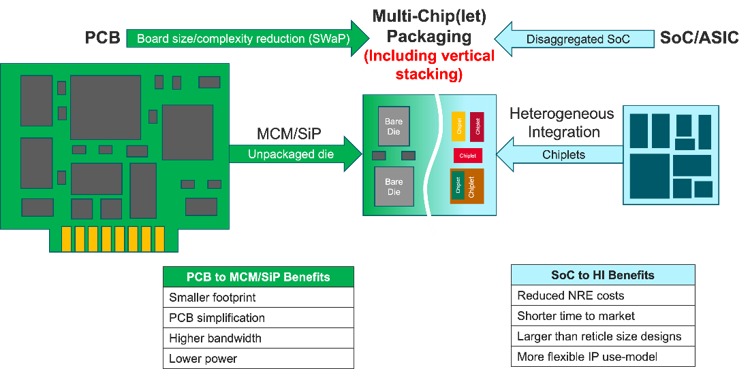

他首先指出,系統級封裝 (即 System-in-Package ,SiP) 有兩個不同的方向。一是把 PCB 上的元件轉移到多晶片組件;二是如同前幾年製造大型系統級晶片 (即 System-on-Chip, SoC) 一樣進行整合,但是轉換制程利用先進封裝來封裝裸片。以下是一些使小晶片 (Chiplet) 解決方案具有吸引力的重要因素:

在為元件挑選最佳工藝節點方面具有很大的靈活性;特別是 SerDes I/O 和類比核,不再需要「全部統一在單一」制程節點上 |

|

由於製造裸片尺寸小,所以良率會更高 |

|

使用現成的小晶片 (Chiplet),可縮短 IC 的設計週期,並降低整合的複雜性 |

|

透過購買良品裸片 (即 known-good-die ,KGD),可普遍降低生產成本 |

|

在許多設計中使用同種小晶片 (Chiplet),時,將具有如同採用批量生產的相同成本優勢 |

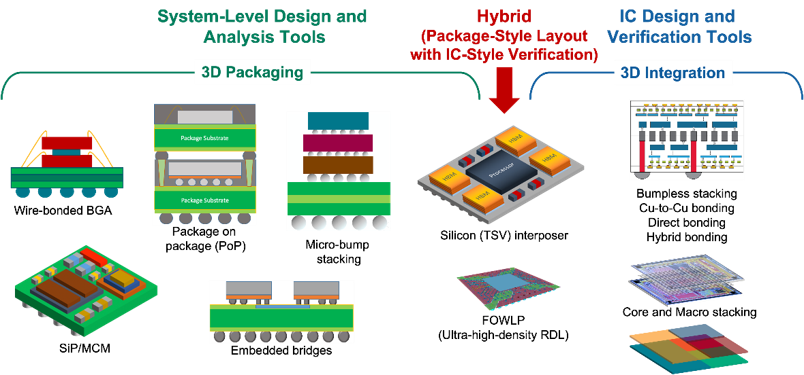

以 IC 為重心的先進封裝改變了設計流程。上圖中,20 世紀 90 年代設計採用的是類似 PCB 的設計流程;而如今已採用類似 IC 的設計流程。把多種不同的技術整合到一起,即 異質整合,結合了多年以來使用的各種制程技術。特別是先進封裝和先進整合方法,例如晶圓堆疊 (Wafer-on-Wafer) 和無凸塊整合 (Bumpless)。

我們可以將 基於封裝 的 3D 視為「後端 3D」,把 先進整合 方式視為「前端 3D」。

後端 3D 是微型凸塊互連 (micro-bumped) 加上每個裸片都有單獨的時序簽核和 I/O 緩衝器。這種方式中,多個裸片之間通常沒有採用協同設計。多年來,這一直是用於記憶體和 CMOS 圖像感測器的常見方法。

對於 前端 3D,裸片通常是直接鍵合的制程工藝 (銅對銅,或採用類似方法)。裸片之間沒有 I/O 緩衝器,這意味著協同設計和分析必不可少,需要時序驅動的佈線和靜態時序簽核 (對於數位設計而言)。所以設計將傾向於朝 Z 軸上佈局,多個裸片會堆疊在一起;這意味著隨著設計的推進,一個特定的區域可能被分配給超過一個的裸片。

這是封裝領域的下一個重要方法轉變,是通往真正 3D-IC 設計的下一步,也就是將眾多不同的裸片堆疊在一起,大大縮短信號所需的傳輸距離。當然,同時也有散熱的問題需要加以分析和管理,因為一個裸片上方的另一個裸片可能起到阻絕散熱的作用,這取決於眾多的設計細節。

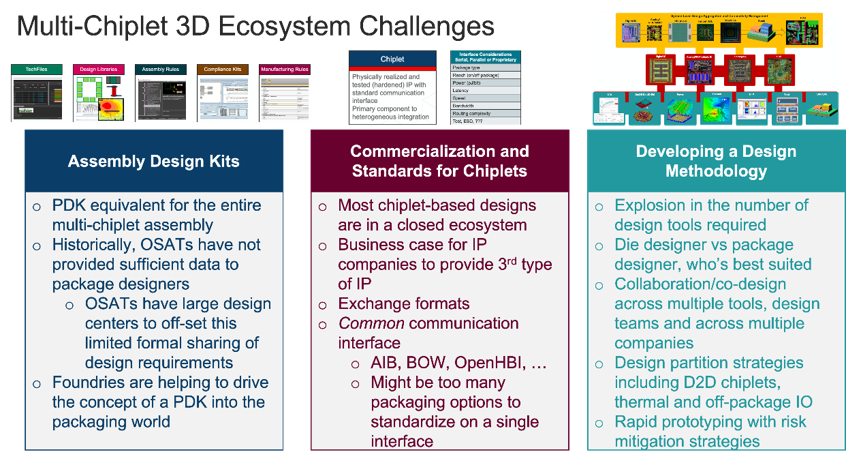

想要使這一新的設計生態成為現實,仍要面臨諸多挑戰,包括組裝設計工具包 (即 Assembly Design Kits,ADK) 的可用性、裸片與裸片互連 (d2d) 的通用標準,以及 EDA 工具的全面支援。

在打造支援這些製造流程的工具時,面臨的一個挑戰是設計規模可能非常龐大,具有超過 1,000 億個採用了多種設計技術的電晶體。這就產生了對高容量、多領域、可進行多技術資料庫相互溝通與轉換的工具的需求,只有這樣,我們才能擁有一個高彈性的通用 3D-IC 解決方案設計平臺。

業界另一個關注領域是小晶片 (chiplets) 的銷售模式。到目前為止,大多數小晶片 (chiplets),除記憶體外,都被設計成單一系統或一組系統的一部分。從長遠來看,就像如今的封裝元件一樣,未來將會有純裸片上市銷售,也會有經銷商 (或新公司) 銷售來自多個製造商的裸片。隨著小晶片 (chiplets) 之間的通訊變得標準化,不僅僅是技術上具備挑戰,商業模式上的挑戰也會應運而生。讓我們拭目以待吧!

3D-IC 有望在網路、圖形、AI/ML 和高性能計算等領域產生廣泛影響,特別是對於需要超高性能、低功耗器件的應用而言。具體的應用領域包括多核 CPUs、GPUs、資料包緩衝器 / 路由器、智慧手機和 AI/ML 應用。

從設計的角度來看,要實現真正的 3D 整合,需要對某些設計工具進行一些加強。尤其在架構分析、熱分析、多裸片間的排置、時序、測試和驗證方面的功能都需要提升。此外,還需要新的系統級功能,如頂層規劃和優化、晶片裸片 (die) 之間和小晶片 (chiplet) 之間的信號完整性和 IC / 封裝協同設計。

想要進一步瞭解 3D 整合和多個堆疊裸片封裝的設計挑戰、生態系統要求和所需的解決方案嗎?

歡迎索取 技術白皮書《3D-IC 設計的挑戰和需求》。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」