By Cadence

在 2021 的 IMAPS (International Microelectronics Assembly and Packaging Society,國際微電子組裝與封裝學會) 大會上,Cadence 資深半導體封裝管理總監 John Park 發表了關於 封裝組裝設計套件 (Package Assembly Design Kits,簡稱 ADK) 的演講:什麼是 ADK,以及 ADK 能為封裝設計帶來哪些好處?

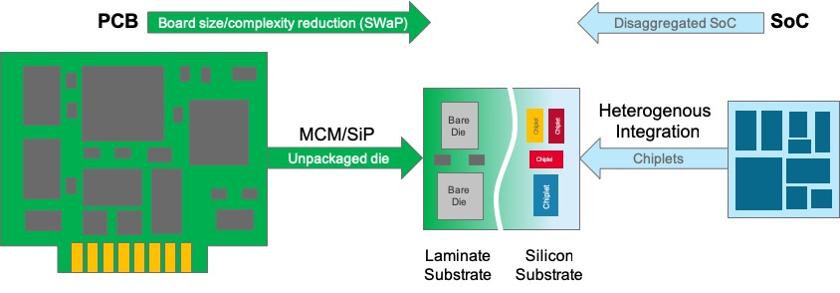

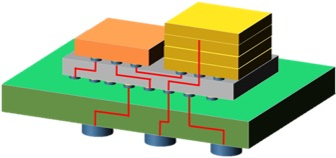

由於異質整合對不同的人來說意義各不相同,John 首先介紹了該市場的發展歷史和趨勢:幾十年來,我們一直在從事多 晶片模組 (Multi-Chip Module,簡稱 MCM) 和類似的整合工作;但在過去五年左右的時間裡,該領域更加專注於 系統級晶片 (System on Chip,簡稱 SoC) 整合——不同於將所有元件都放在一個大晶片上,當前的焦點在於製造更小的晶片,通常稱為「chiplet」,並把它們整合在某種先進封裝中。

這種方法有很多優點,具體取決於設計的細節,其中包括:

降低 NRE (Non-recurring engineering Expense,一次性工程費用) 成本 |

|

加快產品上市 |

|

實現比標線尺寸更大的設計 |

|

更靈活的架構 (多進程) |

PDKs

在 20 世紀 90 年代初創建 PDK (Process Design Kits,制程設計套件) 之前,設計規則檔和用於電路模擬的 SPICE deck 幾乎充當了晶圓廠和設計師之間的介面。隨著工藝變得越來越複雜,設計規則的複雜性也在不斷增加,因此上述做法無法再滿足要求。PDK 的理念是,把 IC 設計者需要知道的關於製造過程的一切知識打包起來,以實現成功設計。PDK 可以被現代 EDA 工具流程所讀取,因此實際的 DRC deck 取代了過去的印刷版 DRC 手冊。

針對封裝設計師的類似 PDK 的解決方案

當設計變得越來越難,需要考慮的方面就越來越多。這導致封裝設計團隊需要考慮的設計方面日益增長:

先進多晶片 (多 chiplet) 、基於矽的封裝需要專門的版圖特徵和形式化的物理 / 邏輯驗證能力 |

|

加特定於矽 (矽) 基板設計的版圖特徵快產品上市 |

|

- 高級淚滴補強和走線加寬 |

|

- 漸進式鋪銅和透氧孔的演算法 |

|

- 大容量設計支援 |

|

來自封裝設計的光罩級精確輸出資料 (GDSII) |

|

- 高級圓弧向量化 |

|

與 IC 實體驗證工具無縫整合,並提供與封裝設計工具間的回饋 |

|

- 光罩級 DRC |

|

- 多晶片 (多 chiplet) 設計的連通性驗證 (電路與佈局驗證) |

|

- 特定區域的高級金屬填充 (平衡) |

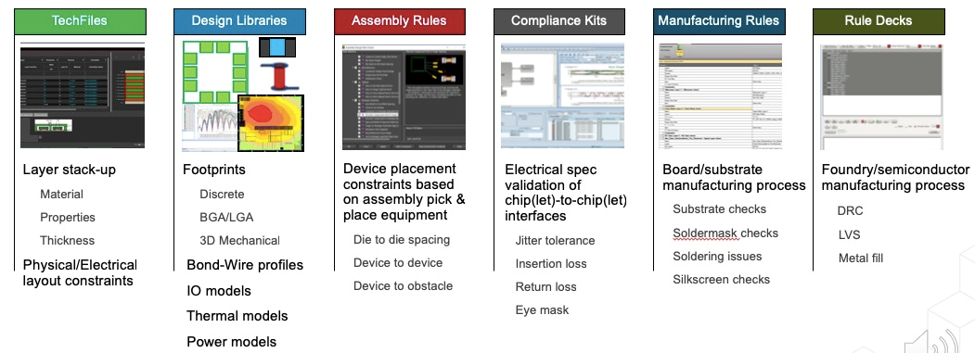

如果想讓封裝設計師在設計中停止猜測,就需要 ADK 封裝組裝設計套件,其工作方式類似於 PDK。但是,一個複雜的問題是,封裝設計師對所有這些矽問題都很陌生,而 IC 設計師對封裝也很陌生。那麼,ADK 中會有哪些內容呢?

上表列出了 John Park 認為應該放在 ADK 中的組件。讓我們分別深入瞭解一下:

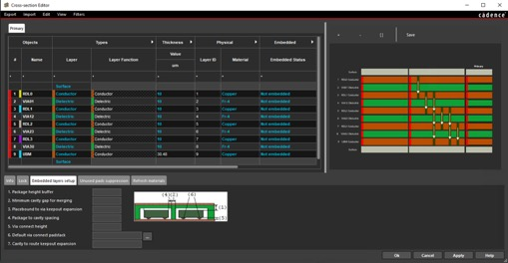

技術檔組件:

這些應該是文字檔,以便於讀取、寫入、比較和共用 |

|

基板堆疊物理和電氣細節 |

|

信號的物理 / 間距約束 |

|

信號的電氣約束 |

|

約束分組 |

|

組裝 / 放置規則 |

|

測試規則 |

設計庫和模型元件:

Footprints |

|

- JEDEC 標準 BGA / LGA 和 SMD |

|

- 焊盤 |

|

- STEP 檔 (真正的 3D 渲染) |

|

3D 鍵合線文件 |

|

- 基於鍵合設備的模型 |

|

- 3D DRC 所需 |

|

I/O 模型 |

|

- 行為 (IBIS) |

|

- 電晶體級 |

|

熱 / 功耗模型 |

|

- 晶片 (小晶片) 級熱和功耗模型 |

|

- 靜態和暫態功耗資訊 |

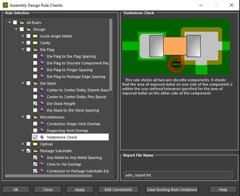

組裝設計組件:

GUI 圖形式介面,簡化設置 |

|

設備獨有的 DFA 概要 |

|

設計同步、直接回饋元件的放置和移動情況 |

|

表格驅動、帶使用者定義的元件類別 |

|

基本模式 (表格) 和高級模式 (約束管理器) |

|

規則定義的設置可以在庫級的單獨工具中完成 |

用於驗證 chiplet 到 chiplet 互連的合規性測試包組件:

基於與 PCB 類似的合規經驗 |

|

抖動容限 |

|

插入損耗 |

|

回波損耗 |

|

眼圖範本 (用於 SerDes) |

規則檢查 (矽仲介層) 元件:

設計規則檢查 |

|

- 包括 3D 堆疊引腳對齊 |

|

電路與佈局驗證 |

|

- 晶片到晶片 (chiplet 到 chiplet) |

|

- 系統級 |

|

金屬填充 |

|

- 智慧金屬平衡 |

抓住機遇,引領市場

對於應當立刻採用 ADK 的原因,John Park 表示:

數十年來,PDK 在 IC 設計界已經得到成功採用 |

|

封裝技術的複雜性呈爆炸式增長,不應該在資訊不充分的情況下盲目設計 |

|

IC 設計師和封裝設計師都面臨新的挑戰,需要新的方法 |

|

封裝設計界應該開始採用 ADK 了 |

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」