By Cadence

每個傳統的封裝設計師都瞭解 電鍍條 (plating bar) 及其作用。為了在製造過程中提供電流,每個 Net 都連接到 BGA 的邊界,以便使電流到達所有需要通電的區域。

電鍍條的定義通常是「圍繞設計邊界的金屬連接」,會略微超出 BGA 的最終輪廓。電鍍條將所有引腳連接在一起,當 BGA 與相鄰的器件分離後,就會移除電鍍條。不會留下任何互連的網路 —— 除非使用蝕刻工藝,去除 BGA 輪廓內部網路之間的短路;這將是一個額外制程步驟。

在 Cadence® Allegro® Package Designer Plus 工具中,電鍍條由兩部分組成。首先,「電鍍條」本身 (外面的導體環) 從封裝邊緣外移,實現全部線路連接。然後,在每個 Net 需要連接到電鍍條器件的地方創建引腳。

如果有引腳沒有連接到電鍍條上,或者如果一個網路在電鍍條器件上沒有對應的一個或多個引腳,制程將會出現問題。

這是一個相當簡單的過程和程式。對於新的設計形式,如矽基板和 system-on-wafer 設計,水準相連 (而不是垂直相連) 透過焊球離開基板邊緣的走線,可能根本就沒有與電鍍條相連。相反,它們可能在一個更大的模式中連接到另一個相鄰的設計器件。

邊緣連接器

在這些設計中確定 Net 的出口 (在哪一層、在封裝的哪一面,甚至是末端的 X,Y 軸位置) 至關重要。如果走線的出口與它在下一個設計器件中的配對連接位置不一致,那麼整個設計將無法正常運行。

此外,網表中需要有器件到器件的連接,以確保沒有遺漏。這也將使介面的映射變得容易管理。電鍍條設計方法不適合表現這種類型的立體連接關係。

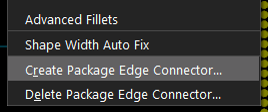

邊緣連接器 (Edge Connector) 是 Allegro Package Designer Plus 中的器件物件,用於創建和配置這些介面。它們可以透過 SI Layout 功能表的 (需要 Silicon Layout Option 的使用權) Create Package Edge Connector 工具製作,如下圖所示:

啟動後,如果不仔細觀察,可能會認為運行的是電鍍條創建工具。這是因為創建電鍍條和邊緣連接器都需要類似的物理幾何形狀。

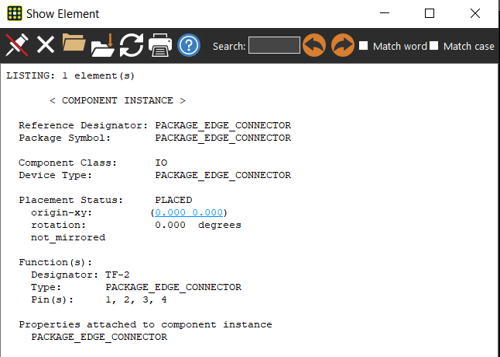

仔細觀察會發現兩者有一些重要的區別。首先,一定要給器件命名。邊緣連接器是一個 IO 類器件,就像 BGA 一樣。它為相鄰器件而不是下一層基板提供 IO。因此,比起電鍍條,參考指示、設備名稱和符號名稱會更加一目了然。

連接對齊

邊緣連接器元件可以提供哪些好處?如果在下一個器件中重複剛使用過的「邊緣連接器」介面,那麼可以確信器件之間走線是對齊的,因為使用了相同資料庫的設定資料。

讓我們看一個簡單的示例。假設我們有一個實例,是一個 10 x 10 器件大型設計中的一個較小的模組,我們希望器件的北側與相鄰單元的南側完全吻合,東側和西側完全吻合。

使用「邊緣連接器」工具,首先,對設計的一側進行佈線。在本例中,我們對東測進行佈線。佈線完成後,生成「邊緣連接器」。然後,使用 symbol edit application 模式,選中東側的引腳。把它們複製到西側,用基板的一個角作為參考點,就可以確信相鄰接的器件兩側完全對齊。

此時,只剩下一個步驟:將正確的 Net 分配給西側的連接器引腳。該操作有助於儘早獲得關於一些可能發生問題的回饋:

是否需要交換晶片介面的引腳,以便對相關的網路進行佈線,同時不需要對「層」做出不必要的更改? |

|

所有的差動對和匯流排的順序都很理想嗎? |

|

延伸到裸片下 BGA 焊球的網路,而不是延伸到相鄰單元的網路,是否應該重新佈設,以避開同一層上交叉的走線? |

|

對於所有的網路,相對於頂層網表,網路和網路的連接是否正確? |

如果能夠回答這些問題,我們就可以確信解決方案是有效的。如果無法回答,可以在設計流程的早期進行最有效的修正。畢竟,返工的代價是我們不願承擔的。

能透過 symbol edit application 模式或 UNFIXED_PINS 屬性移動引腳。設計師不希望在無意間移動或刪除走線。並且走線的端點是鎖定的。

自動佈線

佈線時,佈線工具需要有一個連接起點和終點。

封裝「邊緣連接器」的引腳提供了這些端點。我們可以運行自動佈線工具,任何一個互動式或自動互動式的佈線工具均可,或者也可以運行自己編寫的腳本來進行佈線。如果走線最後可以成功到達邊緣連接器的引腳,那麼走線就是正確的。

最後,由於知道端點在兩個模組中的位置,我們可以計算總延遲、相對延遲等結果。在一個器件中收緊並完成佈線時,可以利用這些結果來更新下一個器件中的允許延遲和容差。逐漸添加和平衡器件的相對位置,並調整到最終的理想位置 (也許需要在某個器件的東側進行添加,而在另一個器件的西側進行添加,以便容納各種新器件)。

為什麼不直接設計一個大型的、扁平化的設計?

如果我們要設計一個 10x10 陣列的模組,為什麼不簡單地把所有 100 個器件並排放在同一個設計中,然後進行整體佈線呢?不採用該方法的理由有很多,其中幾點特別關鍵:

為了更快地驗證變更。因為我們知道每個裸片都是相同的,所以不需要在整個晶圓圖上運行檢查。只需運行一個實例,就可以知道已經找到了95% 或更多的違反設計規則的情況。 |

|

如果在一個實例中出現了違反設計規則的情況,那麼在該實例中進行糾正,便可以糾正所有 100 個單元。因此,只需要修正一次。 |

|

如果設計的下一次反覆運算需要一個 20x20 的陣列,那麼我們對此不需要做任何額外工作,只要在現有的實例中定義一個更大的矩陣即可。 |

|

設計中要關注的專案減少了,在工程變更 (ECO) 上要刷新的實例也減少了,工作效率大大提高。 |

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」