By Cadence

本文要點

為高速 PCB layout 做好準備 |

|

高速設計中的元件擺放和 PDN 開發 |

|

實用 PCB 高速佈線建議 |

為了滿足當今電子產品的需求,數位電路的速度變得越來越快。高速設計曾經是一個冷門的電子產品領域,但如今,大多數產品至少會有一部分需要「高速設計」。這些設計要求 PCB 設計師按照高速規則和要求佈置電路板;而對部分設計師來說,這是一個全新的領域。為此,本文總結了一些最常見的高速 PCB 設計準則,希望對您的高速 layout 設計有所助益。

高速設計的設置

在開始 layout 設計之前,有很多設計和資料庫的細節需要事先處理妥當。

電路圖

雖然在開始設計高速 PCB layout 之前有很多內容需要設置,但大多數人對電路圖都沒有考慮太多。設計師應該驗證元件、模擬電路,並完成設計。但電路圖本身是否已經為 layout 準備妥當?如果設計師不能輕鬆地理解電路的意圖,雜亂無序的電路圖會讓 PCB layout 難上加難。例如,高速訊號路徑需要按順序擺放,以便設計者能夠在 layout 中模擬元件的位置。標記出希望 layout 團隊清楚瞭解的設計區域也很有説明。其中包括:

關鍵的擺放位置,以及某些元件可能需要放在電路板的哪一面 |

|

關鍵零件周圍的禁止佈線區域 |

|

高速佈線資訊,包括佈線拓撲結構、測量長度和匹配長度 |

|

差動訊號對和受控阻抗信息 |

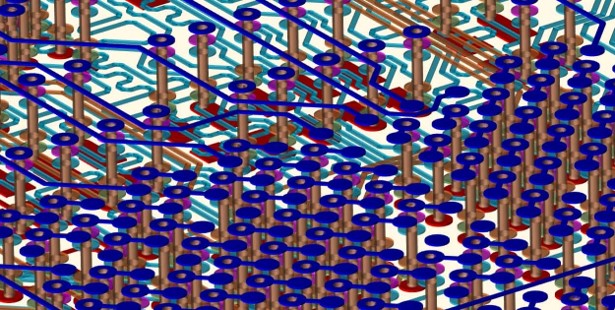

高速電路板的密集佈線

PCB 資料庫

用於高速設計的零件 footprint 必須像 PCB layout 一樣進行檢查和驗證,同時也會涉及一些額外的資料庫方面的工作。例如,為了在高頻或射頻設計中保證訊號完整性,可能需要修改使用的 footprint以減少焊盤尺寸。此外,一些 footprint 可能要縮減到最小尺寸,以適應高密度設計的要求。不過,零件的 footprint 應該盡可能地遵循行業和製造商的規範,以符合可製造性設計 (DFM) 的要求。許多設計工具,如 Cadence Allegro PCB Editor,可以提供線上資料庫瀏覽功能,用於拉取指定供應商的 footprint 模型。

材料和零件

在開始 layout 設計之前,必須選擇用於製造高速電路板的材料。惡劣的工作環境可能需要更堅固的電路板結構,需要使用材料的物理特性來計算受控阻抗佈線:

與製造商溝通,確定電路板是否需要高速材料。 |

|

強化環氧樹脂或 PTFE 材料可能是高速和高頻應用的更好選擇。 |

|

FR-4 的介電常數可能無法保持所需要的阻抗值,或者導致設計出現超出可接受範圍的訊號損失。 |

PCB 零件也需要由製造商進行審查和確認。鑒於當下的供應鏈問題,需要確保在開始設計之前有可用的元件。

板層疊構

高速設計需要特定的板層疊構,以便實現 EMI 屏蔽和訊號完整性。首先要考慮在內部層納入一個完整、連續的接地平面。許多電路板在整個電路板疊構上還設置了多個接地平面層,用於微帶線或帶狀線配置中的多層傳輸線佈線。板層疊構需要在 PCB CAD 資料庫中建立,也可從外部來源導入。在這方面,如果 PCB 設計系統能夠與供應商直接溝通來交換疊構資訊,則會十分有幫助。

設計規則

PCB 設計系統通常有一套非常全面的設計規則和約束條件,可以針對設計進行設置。標準的電路板設計使用零件和網路類來指定間距規則、走線寬度、過孔和其他約束。對於高速設計,應該設置一套全新的規則,包括:

差動訊號對 |

|

訊號路徑 |

|

佈線拓撲結構 |

|

測量和匹配的走線長度 |

|

走線調整參數 |

可以為每個設計設置這些規則;或者在許多情況下,從另一個 layout 中導入,以減輕設計師的工作量。

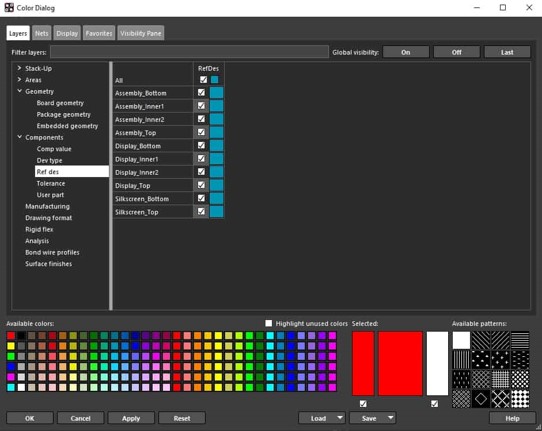

系統參數

設置的最後一項是參數。參數非常重要,包括顯示參數,如顏色和填充模式、網格、佈線偏好和其他一系列參數。透過管理這些參數,設計師可以提高使用工具時的效率。

現在我們已經完成了高速設計的設置,可以開始佈置電路板。

PCB CAD 系統用於設計顏色的參數設置功能表

高速零件擺放的 PCB 設計指南

高速設計的零件擺放依然需要與標準設計擺放遵循相同的規則。為了平衡起見,元件應均勻地分佈在電路板周圍,而且需要遵循製造和測試設計規則 (DFM 和 DFT)。其中包括零件與其他元件、電路板特徵和電路板邊緣的間距。高溫運行的零件應集中在一起,以盡可能多地利用電路板上的區域來散熱,並且必須注意不能阻礙空氣在電路板上的流動。連接器和其他人機介面元件應擺放在技術人員容易接觸到的地方,不同的電源應相互分散放置。

高速設計的不同之處在於,它需要在整個設計中實現最佳的訊號完整性。訊號完整性的主要部分取決於接地平面上有清晰的訊號返回路徑,以及確保數位和類比電路彼此分離。因此,除了要支援所需的走線佈線外,零件擺放還必須確保清晰的訊號返回路徑和電路隔離。為了完成這種複雜的零件擺放,通常最好是在電路板上佈置實際元件之前進行布圖規劃。布圖規劃有助於劃分電路的功能分區,同時不需要不斷地移動元件。

隨著分區一一確定,就該開始擺放零件了。為此我們總結了一些高速零件擺放準則:

在參考平面上為清晰的訊號返回路徑留出空間。 |

|

為密集的資料和記憶體匯流排佈線留出佈線通道的間距。 |

|

避免將元件擺放在類比和數位電路彼此交錯的區域。 |

|

元件擺放的位置要確保高速訊號路徑較短。 |

|

訊號路徑可以包括路徑內的多個零件,要根據電路圖中的佈局來擺放。 |

|

類比元件應盡可能地擺放在一起,以減少它們的走線長度。 |

前文提到,在制定零件擺放計畫的同時,應一同規劃 電源分布網路 (PDN)。接下來,我們來瞭解一些 PDN 的設計建議。

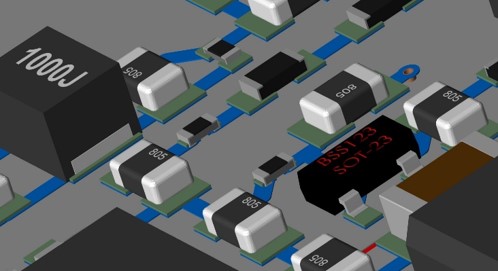

模擬和電源零件的擺放

電源分布網路 (PDN) 設計

在高速電路板中,精心設計 PDN 對電路板的最終電氣性能至關重要。如果沒有清晰的訊號返回路徑,電路板可能會產生大量的雜訊,導致產生錯誤的訊號,干擾電路的正常運行。還可能導致其他訊號完整性問題,如 EMI 和接地反彈。在參考平面上找不到清晰返回路徑的返回訊號,最終可能會耦合到任何它們可以找到的返回路徑上,其中也包括其他走線。這種無意的耦合將產生共模電流,共模電流可能會產生電磁輻射,並帶來額外的雜訊。為了避免這些問題,以下是一些 PDN 設計建議。

使用一個連續的接地平面,不要分割接地平面

使用零件擺放分區來分離數位和類比電路,而不是分割接地平面。 |

|

在對高速傳輸線進行佈線時,確保它們在相鄰的接地平面上有一條清晰的訊號返回路徑。在較高的速度和頻率下,會自然而然地在走線周圍形成返回路徑,因此很容易規劃。 |

謹慎對待可能阻擋接地平面的電路板特徵

在一個集中的區域內有太多的過孔、電路板切口或其他障礙物,會破壞參考平面上的清晰返回路徑。 |

|

避免在鄰近接地平面有空隙的位置佈設高速傳輸線。 |

具有多個電源連接的大接腳數高密度零件

處理器、記憶體和其他大接腳數的高密度零件使用許多電源接腳來滿足其巨大的電源需求。 |

|

在這些連接中,每一個連接都需要一個盡可能靠近電源接腳的旁路電容,以獲得最佳的電源濾波效果。 |

一旦電路板的網路連接和 PDN 實現了最佳配置,就可以開始佈線了。

高速佈線示例,可以看到走線經過了調整

高速走線佈線技巧

當電路板上的零件佈置妥當時,設計將有一個基本的範本,表明走線應該如何佈置。不過需要注意,我們很可能仍然要移動元件,以完善和調整佈線——就像在任何 PCB 設計中一樣。以下是一些高速佈線的 PCB 設計指南:

確保充分遵循線長、匹配長度、寬度、間距、層、受阻抗控制的佈線參數、差動對、走線調整和過孔分配的設計規則和約束條件。 |

|

根據獨特的佈線需求,設置任何必要的區域規則,並留出禁止佈線區域。 |

|

除了特定的佈線拓撲結構和測量長度外,儘量讓佈線盡可能短且直接。 |

|

不要在接地平面的空隙或斷開處佈線。這可能會破壞訊號的清晰返回路徑,並有可能造成前面討論的訊號完整性問題。 |

|

當對高速訊號進行佈線時,要確保它們在相鄰的接地平面上有一個清晰的訊號返回路徑。 |

|

對於敏感的訊號 (如時鐘線和差動對),確保它們與其他佈線之間留有額外的間隙,通常是標準走線寬度的三倍。 |

|

確保將高速傳輸線佈設到它們被分配的層上,以保證它們在相鄰參考平面上的返回路徑。 |

|

避免通過高速傳輸線改變層的屬性,但如果非要這樣做,要儘量使它們與同一接地平面相鄰,以獲得訊號返回路徑。如果層的過渡段比層對更遠,就在訊號過孔旁邊使用一個接地過孔作為返回路徑的過渡。 |

|

謹慎對待相互平行的高速傳輸線,因為它們可能產生串擾。 |

|

注意層與層之間垂直方向的串擾,其間距可能比同一層上並排的兩條走線要小。 |

|

在模擬佈線中使用更寬的走線。 |

|

選擇較寬的網格來放置過孔,為最大數量的佈線通道規劃過孔逃逸。 |

|

儘量減少過孔的使用以減少電感,或者使用盲孔、埋孔或微孔。 |

|

注意不要在分散過孔密集的區域阻斷接地平面上的返回路徑。 |

本文列出的高速 PCB 的設計準則遠非詳盡無遺,但已足夠幫助我們開始著手高速 PCB 設計。另外,記得要充分使用 CAD 工具的功能。除了上文已經談到的設計規則和約束條件外,Cadence PCB 設計工具還有許多其他高效功能,如:

動態背鑽 |

|

背鑽資訊跟隨設計,即時更新。設計調整後,無需手動更新背鑽資訊。 |

|

微孔檢查 |

|

設定鐳射孔相關的設計規則,確保 HDI 設計高品質交付。 |

|

參數化高速結構 |

|

- 無需繁瑣選擇高速結構要素,輸入參數即可生成所需高速結構; |

|

- 在設計中,像使用過孔一樣使用高速結構 (替換、在 Constraint Manager 中設定)。 |

|

3D Canvas |

|

讓設計者看到 PCB 實體,眼前展示的是組裝完成的 PCB。 |

|

DFM / DFA 設計 |

|

不同區域設置不同的 DFM / DFA 規則。 |

|

Allegro Constraint Compiler |

|

將設計指南轉換為設計規則,實現規則同源,説明設計者快速準確複用規則。 |

如欲進一步瞭解更多 Allegro 高速工具應用,歡迎聯繫 Cadence 台灣授權代理商 - 映陽科技團隊。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」