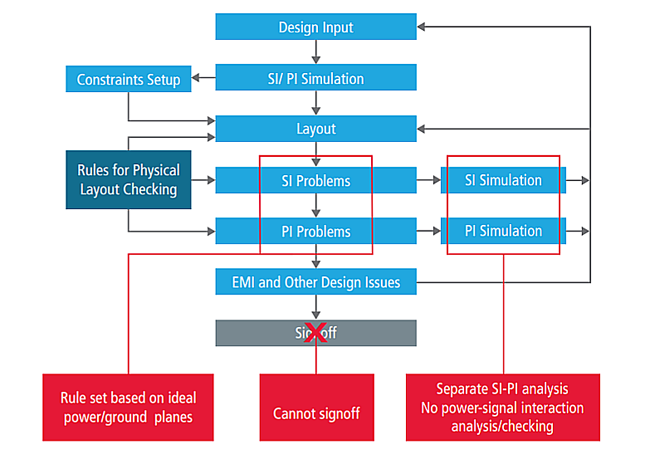

在及時滿足要求方面,負責成功實現 DDR4 和 DDR5 等記憶體介面的信號完整性 (SI) 工程師面臨著重大挑戰。傳統的設計工作流程通常假定配電網路 (PDN) 處於理想狀態,不包含耦合信號、電源和接地平面的不良效應,不會總是對 PCB 的 SI 問題 產生影響。當分別分析電源完整性 (PI) 和 SI 問題時,同步開關雜訊 (SSN) 等基於電源的 SI 問題也會出現,從而導致故障 (圖 1)。

圖 1:通常來說,SI 和 PI 分析是分開進行的,SI 分析假定 PDN 處於理想狀態。

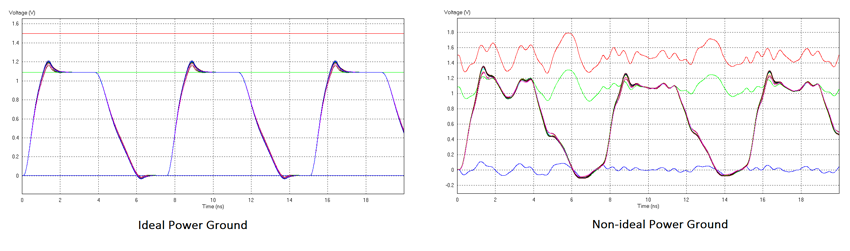

然而,要在高速 DDR 記憶體介面中準確發現 I/O 資料信號 (SI 分析) 以及電源和接地平面 (PI 分析) 的影響,則需要考慮很多方面。事實上,這些並不是人們通常認為的獨立問題;非理想 PDN 總是會影響一些最常見的 SI 分析參數,包括反射、串擾和時序。

什麼是兼顧電源影響的 SI 分析

兼顧電源影響的 SI 分析不僅考慮到了非理想資料信號,而且考慮到了非理想 PDN。例如,PDN 中的雜訊主要影響系統抖動表現——進一步限制了已經非常緊張的 DDR 介面時序預算。

在 2D 模擬中計算特性阻抗時,通常假定電源和接地平面相同。平面彈跳 (也就是整個平面上電源節點與接地節點之間的電勢差變化) 與走線阻抗失配引起的反射耦合。電源 / 接地平面與資料走線之間的任何耦合都會導致串擾。最終,串擾會影響時序,因為它是對能量從一條走線到另一條走線的意外運動的度量。反射也會引起延遲變化並影響時序。

圖 2:理想電源接地與非理想的電源接地

具有非理想電流返回路徑的 DDR4 和 DDR5 資料匯流排上的同步開關信號會導致 SSN。並行資料線中的每一個比特都彼此獨立工作,當信號同時觸發時,可能導致電源上的負載加大。這種「同步開關」會導致電壓下降,進而使設備內的接地電壓升高至非零值。

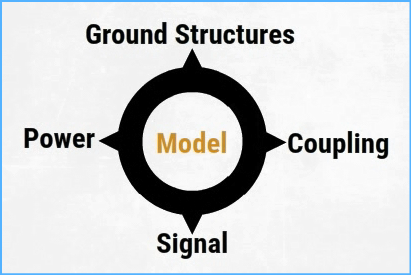

最終,SSN 會對眼圖隨機抖動分析產生不利影響,並對優化 DDR 記憶體的系統雜訊容限造成更多限制。通常來說,SSN 分析只能由分析工具透過使用特殊的 I/O (兼顧電源影響的 IBIS 5.0+) 模型和互連模型 (耦合信號、電源和地面) 來執行。

IBIS 5.0+ 模型可以根據記憶體控制器和記憶體提供商來推斷,而兼顧電源影響的互連模型提取自完整的設計。傳統的 SI 工具沒有配備合適的場求解器來充分完成 SSN 分析任務。此外,一旦將設計完全佈局並進行佈線,就很難在滿足截止日期要求的前提下進行修改和優化。

大多數商業模擬平臺採用傳統的設計規則檢查程式,沒有考慮到信號的雜訊影響,僅進行幾何規則檢查。這使得在設計同步分析和佈局後分析期間很難檢測到任何有違設計約束的「兼顧電源影響的」方面,或者很難對 SI/PI 問題進行微調。

以下內容更加詳細地討論了兼顧電源影響的 SI 分析中每個流程步驟的處理方式。

兼顧電源影響的設計規則檢查程式

許多工程師喜歡使用全波 3D 工具進行互連提取,但通常來說,兼顧電源影響的分析使用由混合求解器創建的 S 參數。工程師經常求助於利用場解決方案、電路等效模型或同時利用二者的混合求解器。借助類似於時域 SPICE 的模擬器,可以從透過模擬獲得的頻率回應中提取出簡單的集總元件 (RLC) 寬頻 SPICE 模型,從而簡化無源輸入 / 輸出系統行為的數學描述。

儘管全波 3D 方法大大放緩了獲得模擬結果的速度,但是卻往往降低了較高頻率下的建模精度,對於 DDR 介面中具有複雜結構的十億位元通道來說更是如此 (例如蛇形線、過渡、背鑽等等)。此外,從大型互連模型中提取時域模擬可能會導致收斂問題,因為 S 參數模型在 DC 上沒有資訊,並且在較低頻率下可能無法運行。

「切割和縫合 (cut and stich)」方法為耗時較久的 3D 全波求解器和精度較低的混合求解器提供了替代選擇。該方法對目的地區域進行分區,工程師可以隨心所欲地選擇求解器對 PCB 的一部分進行精確建模。這樣一來,需要更複雜分析的 PCB 部分可以使用 3D 全波建模,而其它部分則可以使用混合工具來節省建模時間。儘管這種方法確實節省了模型生成的時間,但為了弄清楚基於電源的 SI 變化,工程師每次對佈局進行校正調整時,仍然需要提取 SPICE 模型。

FDTD 方法

時域有限差分 (FDTD) 方法不必提取 S 參數,避免了隨之而來的潛在收斂問題。FDTD 方法與混合求解器一起使用,以獲得時功能變數結果,包括信號、電源和地面之間的相互作用。

Sigrity SPEED2000 引擎可從 Sigrity SystemSI 直接使用,該引擎使用搭配混合求解器的 FDTD 直接方法,整合了電路求解器、傳輸線求解器和快速電磁 (EM) 場求解器,以分析資料和電源 / 接地平面之間隨時間變化的相互作用 (圖 3)。線性激發作用於大量的信號網,以反映耦合雜訊下的信號品質。這不需要大型 S 參數檔和非線性分析,資料準確性不會受到影響。

圖 3:要評估同步開關雜訊 (SSN),互連模型必須包括信號、電源、接地結構以及它們之間的耦合。

使用 FDTD 方法的混合求解器增強了提取時的傳統設計工作流程,允許工程師快速分析和評估任何兼顧電源影響的 SI 問題,而無需重複進行模型提取。這最終在 PCB / IC 封裝層面上產生了更加準確的模擬結果,兼具準確性和速度,並縮短上市的總體時間。

例如,在 DDR 介面中,這種方法的優勢顯而易見。在這種介面中,高佈線密度在滿足串擾、時序、成本和空間限制的同時,帶來了長度匹配、間距和資料信號分組等複雜的佈局問題。堅持保守的線長和間距可以滿足串擾和時序要求,但會加大電路板面積。

另外,由於模擬中包含大量的 DDR 信號、DDR 電源 / 接地網和開路,傳統的 SPICE 時域模擬通常具有更明顯的無源性和因果性問題。使用混合求解器實施 FDTD 方法能夠提供更準確的、與實驗室結果相匹配的模擬結果,從而加快上市時間,並借助完整 DDR 匯流排界面的 3D 模型提高最終的簽核水準。

3D 全波建模的最終簽核

為了提高準確性,需要提取帶電源和接地平面的完整記憶體匯流排。對於大多數 3D 全波建模工具而言,這通常是一件過於艱巨的任務,會引發收斂和穩定性問題,因為先進的多晶片 DDR 介面可能涉及數百個埠的模擬。

在有限元法中,通常是將解決方案擾動成更小的時間步長來實現收斂,在權衡模擬時間的情況下產生更加平滑的輸出曲線。隨著模擬過程的逐步進行,穩定性與誤差的衰減有關。為了使偏微分方程的解與離散化過程得到的計算解達成一致,這個解需要同時表現出穩定性和收斂性。

由於缺乏足夠的計算資源來充分類比大型 DDR 介面,選擇使用 3D 全波提取的設計人員經常將其設計細分為更小的部分。這需要高水準的專業知識,並且容易出錯。此外,該方法通常不適合反覆運算設計過程——如果對佈局進行了更改,則必須進行模型提取,然後重新運行模擬。

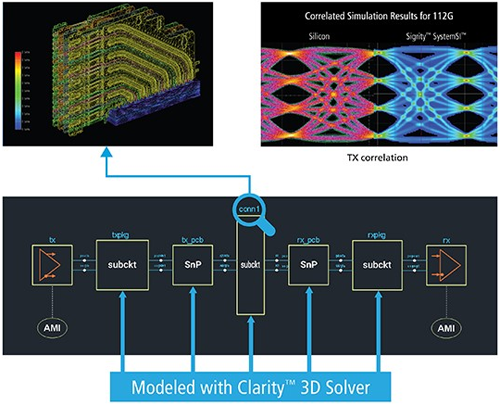

Clarity 3D Solver 的問世改變了這一切。與傳統的場求解器技術相比,Clarity 3D Solver 可提供更快的模擬性能和無限容量(圖 4)。經過優化,Clarity 3D Solver可將作業分發到多台低成本的電腦上,並且與在更強大、更昂貴的大記憶體伺服器上運行時同樣高效。

圖 4:Clarity 3D Solver 實現可用計算資源與設計規模的有效匹配。

得益於此,Clarity 3D Solver 可以創建高度準確的 以用於 SI 和 PI 分析的S 參數模型。此外,Clarity 3D Solver 消除了手動縮小建模結構尺寸的風險。

結論

隨著資料速率提高到十億位元速度和時序預算收緊,DDR4 和 DDR5 介面涉及到工程師們當今面臨的最具挑戰性的 SI 問題。數十億位元的平行匯流排介面涉及下降的電壓擺幅、均衡的收發器,嚴格的誤碼率 (BER) 要求以及匹配的傳輸線長度。為了滿足嚴格的時序約束,必須瞭解非理想 PDN 對 SI 的影響。

傳統的 SI 分析工作流程往往十分繁瑣,因為兼顧電源影響的 SI 分析通常是在佈局後進行,佈局的每一次更改都需要重複進行模型提取,以便充分瞭解電源和地通路波動對 SI 的影響。經過驗證的從前端到後端的流程將最大程度地減少設計反覆運算,並有助於按時、按預算將產品推向市場。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」