Paul McLellan, Cadence

你聽說過 IBIS 和 AMI 嗎? 如果我們在法國,那麼 IBIS 是一家酒店的名字,AMI 則是我對你的稱呼——朋友。

但是如果我們在談論 SerDes 設計領域,那麼 IBIS 和 AMI 就是對 SerDes 通道進行建模的方式,可以在保證設計性能的前提下,確保信號成功地在不同晶片之間進行傳輸。

然而當下,我們的行業正面臨著巨大的變化,IBIS 和 AMI 的含義需要被更多設計領域的人瞭解。DFE 均衡(判決回饋均衡)即將被規定包含在 DDR5 標準之內,這將需要運用IBIS + AMI 進行建模,從而設計出諸如新一代 DIMM、能夠承載 DDR5 DRAM 的系統。

IBIS

IBIS 代表 I / O 緩衝器資訊規範,創建於 20 世紀 90 年代初。那時,信號完整性問題剛剛開始受到關注,Quad Design 公司製作了第一個成功商業化的信號完整性工具,包含專有模型和元器件庫。 1993 年,Intel 公司決定摒棄大量專有元器件庫的方式,邀請包括 Cadence 在內的其它公司進行合作,共同制定通用標準。當時,Intel 正嘗試為全新 PCI 標準制定驅動程式要求。此次合作結果為業內奠定了最初標準——IBIS 1.1。該標準涵蓋了上拉和下拉電晶體及其轉換時間、鉗位二極體(用於壓制反射)以及封裝引腳模型(包括電感、電阻和電容);無論有沒有驅動電晶體,輸入模型也將是相同的。IBIS 2.1 版本在 1994 年成為 ANSI / EIA 標準,自此之後便進一步發展著。

均衡

上圖描述的即是均衡問題。理想化的輸入位元流是一個完美的方波。 由於通道在不同頻率存在不同程度的衰減,到達接收器的信號則會非常失真。因此,輸入信號的時鐘和資料就必須被重新恢復。

多種形式的均衡皆可用於應對通道中的信號損失。在信號發送端,預加重或去加重可以補償通道損失。例如,預加重通常會增強信號的高頻分量以彌補通道將會減弱大部分信號的事實。通道本身由封裝引腳和電路板走線組成,因而無法對其進行任何主動改變,而被動效應則需要建模。

在信號接收端,自動增益控制 (AGC) 首先將輸入信號提高到足以檢測到的強度,連續時間線性均衡 (CLTE) 再對符號間的干擾 (在相鄰兩位元資料之間) 進行消除。而真正智慧的技術 (以及大部分區域和電源) 則在於時鐘資料恢復 (CDR) ,CDR 從輸入的類比信號中重新生成時鐘;以及判決回饋均衡 (DFE) ,DFE 使用 FIR 濾波器,並自我調整調整抽頭係數。這一技術方法需要良好穩定的信號,因此 AGC 和 CTLE 被放置在接收器的前端。

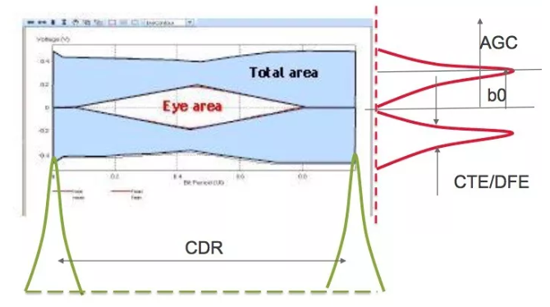

如上所示的眼圖,橫坐標為時間,縱坐標為信號電壓。綠色高斯函數表示 CDR 匯出時鐘轉換的位置,紅色高斯函數則表示 1 電壓和 0 電壓的分佈狀況(二者單獨分佈)。

只要重新恢復的時鐘的中點接近眼睛的中心,並且 DFE 使兩個紅色峰值保持分離又緊密相連的狀態——這意味著它能夠正確辨別出電壓值 1 和 0 之間的 b0,圖示中間的眼睛就會打開。顯然,如果時鐘恢復漂移得太遠,或者 0 和 1 電壓過於接近——即使只是偶爾才會出現如此狀況——比特誤碼則會產生,而眼睛也將關閉(當數百萬信號重疊時)。

AMI

AMI,演算法建模介面,是為實現更好地通道建模而在 2007 年對 IBIS 進行的擴展。Cadence 在推動 AMI 標準化流程方面處於領先地位。 AMI 中的「演算法」是指它是可執行代碼 (可以用任何語言編寫,C 語言最為典型),並與傳統的 IBIS 電路級模型共同工作。通過使用編譯代碼,而不是像 IBIS 這樣的文字檔,AMI 允許用戶更深入地訪問片上技術而無須擔心洩露任何「秘密資料」。由於通常發射端與接收端製造商並不相同,AMI 可實現隨插即用模擬。

不同於並行鏈路,高速串列鏈路不需要大量引腳並成為了資料進出晶片和記憶體的主要方式。然而,它卻需要大量的資料流程量被進行模擬,這就是 AMI 所要解決的問題。而大量資料流程量需要被模擬的原因有三:

1. |

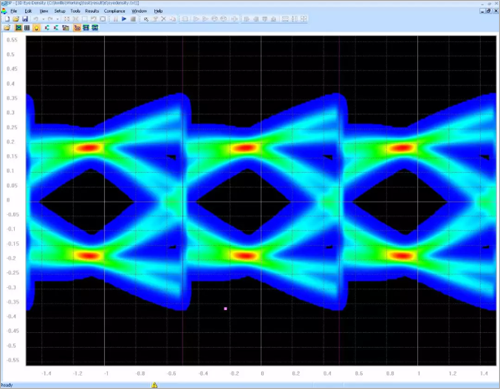

確保鏈路可靠地工作需要創建眼圖 (如下圖所示)。為了保證眼圖睜眼則需要模擬大量資料,一方面確保信號總是遠低於或高於眼睛,另一方面確保重新生成的時鐘精準到足以使中點位於眼睛的中心。 |

|---|

2. |

串列鏈路的主要特點是誤碼率 (BER),其在 10-12 或 10-16 的情況下可為 1。使用 SPICE 也許可以模擬幾百位元資料,但通常而言要獲得精確估計的 BER 則需要模擬一百萬位元資料。 |

|---|---|

3. |

十年以來,資料速率已從 2.5 Gbps 提高到 25 Gbps,並且將很快提高到 120 Gbps。 隨著未來的設計水準不斷提高,400 Gbps甚至 1 Tbps(1000Gbps)的資料速率指日可待。信號編碼已經從單眼發展到多眼 PAM4,這就對設計精度提出了更高的要求。基本要求是需要用非常快速和精確的均衡模型來模擬非常大的位元流。 AMI可以完全滿足此項要求。

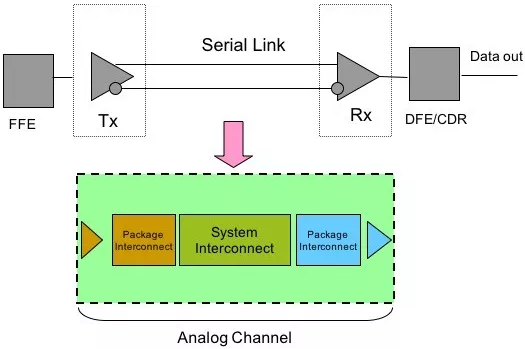

串列鏈路的信號完整性分析由三個階段組成:首先表徵通道,然後執行大位元流通道模擬,最後對輸出進行後處理以檢查睜眼情況和 BER 值。

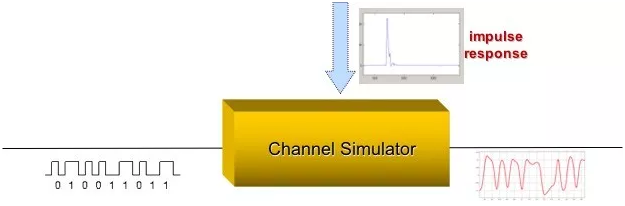

表徵通道由脈衝回應實現。 輸入一個階躍信號,並使用電路模擬器獲得階躍響應,進而推導出脈衝回應並捕獲驅動器和接收器之間的任何互連行為。

通過將脈衝回應與位元流卷積產生原始波形,實現通道模擬。即使在進行複雜的自我調整均衡時,數百萬位元資料的模擬也可以在幾分鐘內完成。上圖展示了這些部分的聯繫。

DDR5

正如前文所言,預計在今年夏季發佈的 DDR5 標準中,DFE 功能將被正式規定包含在 DRAM 中。這意味著你將急需一個 AMI 模型。 你打算怎麼做?你是否在考慮有沒有比打開文字編輯器進行編碼更簡單的方法?

我們將在後續文章中想你所想、解你所急,敬請期待 !

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」