By Ken Willis, Cadence

隨著電子行業技術的發展,特別是在傳輸介面方面,從 PCI 到 PCI Express、從 ATA 到 SATA、從並行 ADC 介面到 JESD204、從 RIO 到 Serial RIO 等等,無一都證明了傳統平行介面的速度已經達到瓶頸,取而代之的是速度更快的序列介面,於是原本用於光纖通信的 SerDes 技術成為了高速序列介面的主流。序列介面主要應用了差分信號傳輸技術,具有功耗低、抗干擾強,速度快的特點,諸如 PCI Express®(PCIe®)Gen4 等串列鏈路介面的資料傳輸率將達到雙位千兆級傳輸速率。由此,器件建模、互連建模和分析方法必須不斷發展,以應對不斷減小的設計餘量和當今工程師面臨更具挑戰的合規標準。本系列文章將從各方面深入分析探討,為了降低風險並優化設計,將分析盡可能地推向上游至關重要,以實現權衡、可行性研究、元件選擇和約束獲取。

由於諸如 PCI Express®( PCIe® )Gen 4 等串列鏈路介面的資料傳輸率將達到雙位千兆級傳輸速率,器件建模、互連建模和分析方法必須不斷發展,以應對不斷減小的設計餘量和當今工程師面臨更具挑戰的合規標準。為了降低風險並優化設計,將分析盡可能地推向上游至關重要,以實現權衡、可行性研究、元件選擇和約束獲取。

鏈路中,SerDes 發射器和接收器的均衡地精確建模對於獲得更好的模擬結果至關重要,這包括幾乎所有高資料速率串列鏈路中存在的複雜自我調整均衡。隨著過孔陣列需要全波 3D 的解決方案,以便透過過孔 stub 和耦合行為準確地表徵其複雜性,互連模型也面臨新的挑戰,這可能會需要幾分鐘到幾小時或幾天的提取時間。模擬之後,經常需要介面特定的後處理來檢查發射器、傳輸同道和接收器的合規性。

接下來將介紹創建串列鏈路預設計「 虛擬原型 」的方法,及如何創建與之相關的互連和 SerDes 模型。我們將檢查如何使用 IBIS-AMI 模型,以及如何在沒有現有模型使用的情況下創建自己的模型。它還將向您展示最新的互連提取技術,以便在控制計算時間的同時保證「您需要的全波精度」,及如何使用基於標準的合規工具來自動執行佈局後分析和高級介面驗收,如 PCI Express Gen 4。

簡介

隨著資料速率的不斷加快和電源電壓的不斷減小,用於解釋邏輯的「單位間隔」或「UI」受到了明顯的壓縮。

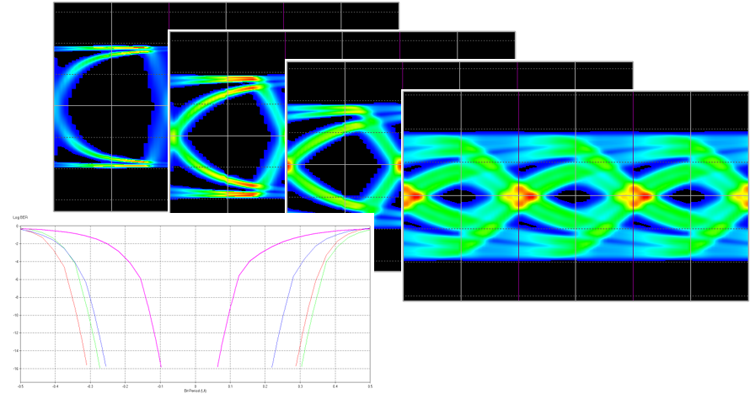

圖 1:各種 PCI Express 資料 8’’ 運行通過 FR4 帶狀線

隨著工作空間越來越小,將信號完整性(SI)分析過程進一步推向上游變得越來越重要,以便在設計過程中更早地定位問題、應對挑戰,從而減輕流程後端的風險。 這需要傳統方法的一些轉變,以及用於建模串列器/解串器或用於發送和接收高速信號的「SerDes」器件的新技術。 這種前期的勞動成果包括設計中優化的材料清單(BOM),以及實現約束驅動印刷電路板(PCB)物理佈局過程的約束。 結合高效的佈局後互連提取和自動化合規檢查,能夠確保給製造商驗收您的設計,沒有意外或進度影響,並在硬體方面取得成功,同時避免昂貴又耗時的重工。

透過「自上而下」的方法將SI推向上游

成功實現能夠達到這些資料速率的關鍵因素之一是在傳統的佈局後驗證步驟中將 SI 分析起點更多地推向上游。這裡有一個錯誤的概念,在傳統的「自下而上」方法中,直到經過詳細的 PCB 佈局後才能進行有意義的分析,然而在實際硬體設計環境中並非如此。

當設計工程師完成 layout 後,通常有一兩天的時間,來自各個學科的工程師(機械、熱、信號完整性、電源完整性、EMI)可進行最終檢查,為最後的 layout 提供一些改進意見。但是,通常要承受來自專案經理的巨大壓力,要在規定的時間段內將 Gerbers 交給 PCB 製造商,而組裝廠將按序訂購元件並接收這些裸板進行裝配和測試,軟體工程師將會等待硬體進入實驗室,以便他們可以測試最新的軟體版本。換句話說,在 PCB layout 初步完成時,供應鏈依賴性的多米諾骨牌效應將被完全捕獲於專案經理的甘特圖中,而在這一點上執行詳細 SI 分析的可用時間將很短。通常更可能的是,「運行分析,直到時間耗盡,然後發貨」,而不是「運行分析,直到您滿意,介面工作正常,然後發貨」。

為了在該 PCB 設計流程的壓縮後端完成關鍵節點的簽收,準備工作至關重要。一個策略是「 自上而下 」,提前于後期,建立一個早期版本的串列鏈路介面模擬測試台。當您初步瞭解用於發送和接收信號的 SerDes 和協定( 例如 PCI Express Gen 4 )時,可以在早期 BOM 階段開始從上游進行詳細的電路圖設計,這是解決系統磁碟分割、多少個 PCB 將用於構建信號路徑、以及將用到什麼樣的連接器的一般方法。系統中所有模組的具體詳細模型在這個早期階段並不重要,最初可以使用「 現有模型占位元 」,但是在瞭解更多詳細資訊的情況下,它們將被替換。( 合規工具包含搭建早期測試平臺所需前期模型的豐富來源,將在後續部分中介紹。)簡而言之,如果您可以在餐巾紙上繪製介面,那麼您應該就能夠早日整合模擬測試平臺。這種自上而下的方法有很多好處:

可使您視覺化整個系統和將被遍歷的信號路徑。 |

|

可以說明您確定完成所有晶片間信號路徑連接所需的所有模型,以備用。 |

|

提前運行一些步驟,使您可以提前搭建模擬測試平臺,從而整個過程中的後續工作主要是更新拓撲中的模型、更詳細地重新運行模擬。當時間緊張時,這個過程的後期可以節省大量的時間。 |

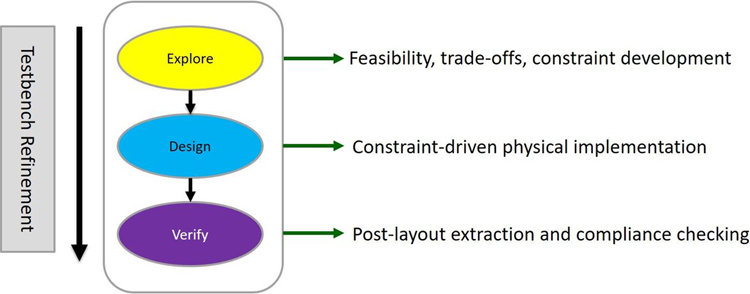

圖 2 :一般設計方法

隨著串列鏈路拓撲的初始原型拓撲,並且各個模組至少存在現有初始模型,您應該擁有一個測試平臺,用來模擬,並以目標資料速率傳遞流量進行分析。現在,在您的設計過程中,將逐漸開始使用更具體、更真實的模型替代初始模型。這些模型通常有以下幾類:

SerDes 發射器和接收器的IBIS-AMI模型 |

|

分立器件的 Spice 模型(例如 AC 去耦電容) |

|

封裝 |

|

PCB 走線 |

|

PCB 過孔 |

|

連接器 |

第一步是在拓撲中各模組所需的模型以及在庫中的現有模型之間進行差距分析。用現有模型增強測試平臺,並驗證模擬結果。接下來,列出缺少的模型,聯繫模型供應商(可以是內部的或者外部的),並提出模型需求。記錄連絡人、聯繫日期和模型的狀態。當您得到它們後,就可相應地增強您的測試平臺了。

文章出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」