By Ken Willis, Cadence

IBIS-AMI建模

假設我們的 PCIExpress Gen 4 串列鏈路,使用初始的 PCB 走線和過孔模型,其餘的缺失部分用於發射器的IBIS-AMI 模型,「AMI」表示演算法模型介面。正如其名,IBIS-AMI 模型具有以傳統 IBIS (I/O 緩衝區資訊規範) 格式定義的「電路」部分和以 AMI 格式定義的「演算法」部分,兩者都是完整模型所必需的。

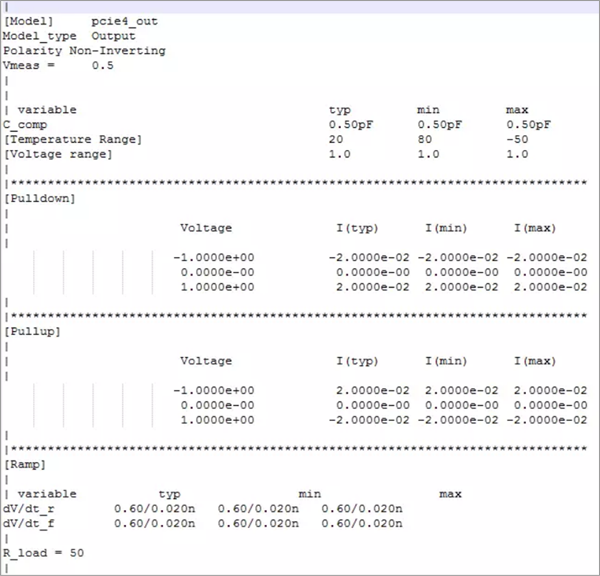

該模型的電路或 IBIS 部分用於描述發射器的電壓擺幅、輸出阻抗、寄生效應和上升 / 下降時間特性。這些資訊應該在您 SerDes 發送器的資料表中。假設資料表顯示,以 50ohm 作為參考阻抗,擺幅為 1V,單端 50 歐姆輸出阻抗,0.5pF 範圍內的焊盤電容,以及 20ps 左右的單端上升 / 下降時間。採用一個標準的 IBIS 模型作為開始,是最直接的做法。

圖 1:初步的 IBIS 模型

該演算法(或模型的 AMI 部分)用於描述發射器的均衡行為。在 PCI Express Gen 4 的情況下,這由前向回饋均衡(FFE)或「去加重」組成。FFE 將包含多個「抽頭」,表示產生去加重行為的 main 和 boost 驅動器,boost 轉換位(例如 0 到 1 的轉換)和去加重穩定狀態位元(例如連續的多個 1)。這些抽頭的作用大小通常用係數來表示,表示與主抽頭相比它們的比例係數。

圖 2:含 PCI Express 預設的 FFE 和發射器波形

將上述資訊作為輸入,現在的 IBIS-AMI 模擬工具通常包括直接生成 AMI 模型的功能。同樣,這些資訊通常可以在 SerDes 發射器的資料表中找到。假如您感興趣的發射器使用與 PCIExpress 規範中描述的類似的去加重設置,可以使用如前所述的自動化工具,利用上述的抽頭係數快速直接地生成 AMI 模型。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」