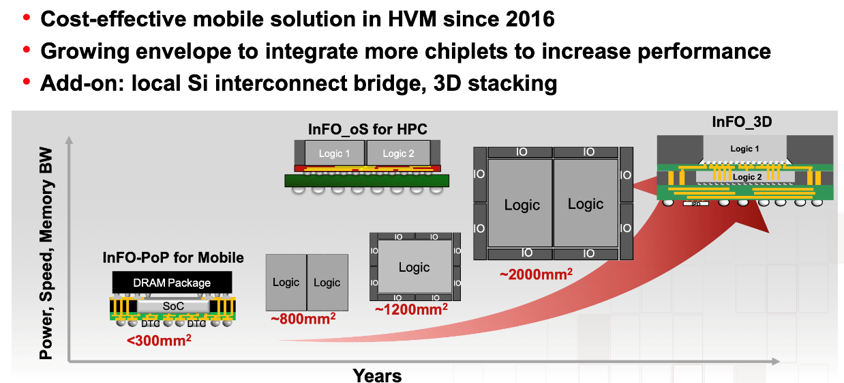

在 2022 年底舉辦的 TSMC OIP 研討會上,Cadence 資深半導體封裝管理總監 John Park 先生展示了面向 TSMC InFO 技術的先進自動佈線功能。InFO 的全稱為「整合式扇出型封裝 (integrated fanout)」,是一種適用於先進封裝的低性能、低複雜度的技術。下圖是 TSMC 演示文稿中一張介紹 InFO 的投影片,不難發現,InFO 有許多不同的類型。

InFO 的首個應用實例出現在 2016 年,是用於行動應用的 InFO-PoP,在應用處理器晶粒上添加了一個 DRAM 封裝。然後是面向 HPC 的 InFO_oS,允許將多個晶粒置於越來越大的封裝中。最新的技術是 InFO_3D,允許邏輯和邏輯之間垂直堆疊,並在下方佈線,以便分配供電網路和訊號。

在本文中,我們不打算重申使用先進封裝的優勢,而是進行擴展,假設以採用最先進的節點為前提來進行設計。

如前文所述,先進封裝和異構整合如今已成為所有半導體設計的熱門話題。

佈線已成為先進封裝技術的主要瓶頸

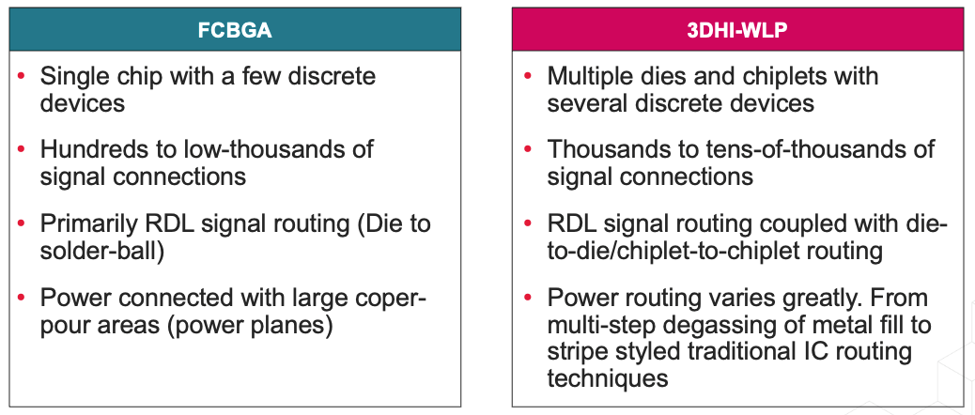

從上表中可以看出,如今的佈線難度越來越大。左側是倒裝晶片球柵陣列 (FCBGA) 的要求,其中最多有幾千個連接。RDL 訊號佈線將訊號從相對較小的單個晶粒分散到焊球上。

右側是本文將要討論的技術——3D 異構整合晶圓級封裝 (3D heterogeneous integration wafer-level packaging),簡稱 3DHI-WLP。這種封裝通常包含多個 chiplets 小晶片,並可能存在數萬個訊號連接,因此 RDL 訊號佈線不僅是分配訊號,同時也要處理從小晶片到小晶片 (chiplet-to-chiplet) 的佈線。電源佈線同樣錯綜複雜,多種方法均可實現。

在細節層次上,業界面臨的挑戰有:

小晶片到小晶片和扇出 RDL 佈線要求 |

|

高效的接腳逃逸模式 |

|

佈線通道密度 |

|

複雜過孔堆疊 |

|

提高良率的互連倒圓角 |

|

將訊號和電源網路放在一起進行佈線,以達到最佳密度 |

|

支援可重複模式再利用 |

|

電源 / 接地過孔放置 |

為了應對這些挑戰,Cadence 和 TSMC 通力合作,為 InFO 技術開發新一代自動訊號佈線解決方案:

支援高容量設計的多執行緒自動佈線引擎 |

|

支援 TSMC 電氣、物理和良率規則的佈線 |

|

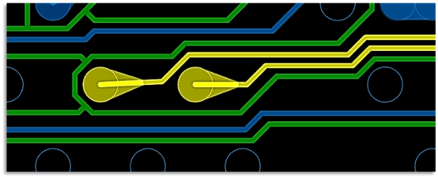

支援屏蔽、差分訊號和倒圓角 / 淚滴插入 (見上圖) |

|

帶有複用結構的預先逃逸佈線 |

|

基於分片的佈線,支援複製 |

自動電源佈線解決方案:

混合和匹配 IC 樣式及 BGA 樣式的電源佈線 (條紋 / 軌道和平面) |

|

鎖定結構,防止在相鄰區域工作時發生變更 |

|

可保存的配置,可用於後續設計 |

|

根據電源接腳的分組,自動定義形狀邊界樣式 (拼圖) |

綜上所述,流程是:

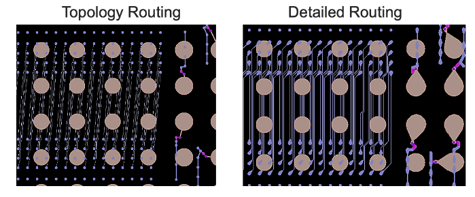

拓撲結構佈線 |

|

逃逸佈線 |

|

電源佈線 |

|

詳細佈線 |

|

模式複製 |

|

倒圓角插入 |

|

最終 DRC |

結果

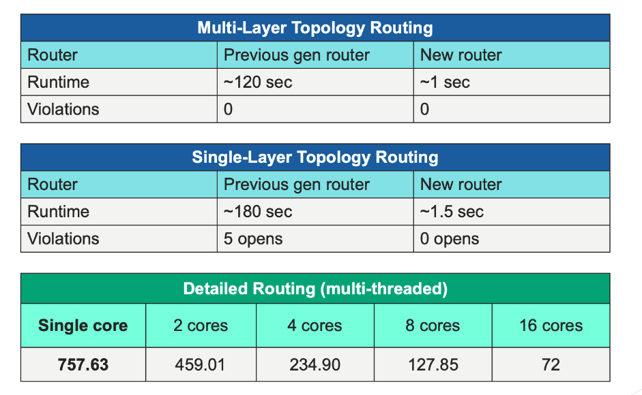

如上表所示,佈線速度大大提升 (100 倍)。使用多核心多執行緒詳細佈線也能使速度提高 10 倍以上。

總結

1. |

當下普及先進封裝技術的主要瓶頸在於佈線 |

|---|---|

2. |

訊號佈線 (RDL / D2D) 和電源佈線也是如此 |

3. |

需要新一代的解決方案來減少瓶頸並支援大型設計 |

4. |

Cadence 和 TSMC 已經合作開發了用於 InFO 封裝技術的新一代訊號和電源自動佈線工具 |

a. 原生大規模並行化 |

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」