在當今的封裝設計產業中,設計複用 (Design Reuse) 是加快設計週期的關鍵,因為上市速度決定了產品能否大獲成功。大多數的封裝設計都可能採用 打線接合 (wire bonding),因此可以在不同的設計中共用打線接合資訊非常重要。然而,設計複用和 ECO (Engineering Change Order,工程變更命令) 可能會造成與打線接合相關的封裝設計問題,從而影響設計完整性,有時還會在設計過程的後期階段導致設計失敗。

Cadence Allegro Package Designer Plus 工具集提供了強大的檢查功能,可以發現設計中的此類問題,並盡可能自動解決這些問題。本文將詳細探討這些針對打線接合的設計完整性檢查。

運行打線接合相關的封裝設計完整性檢查

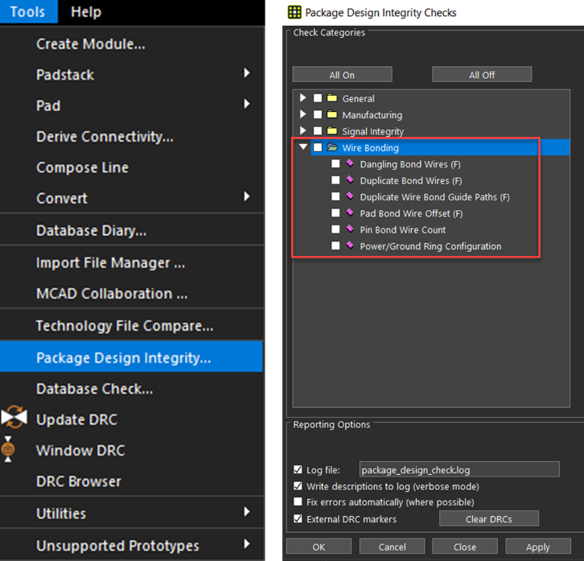

在 Allegro Package Designer Plus 中運行封裝設計完整性檢查:

1. |

選擇 Tools ─ Package Design Integrity: |

|---|---|

2. |

選擇 Wire Bonding 檢查並點擊 Apply: |

3. |

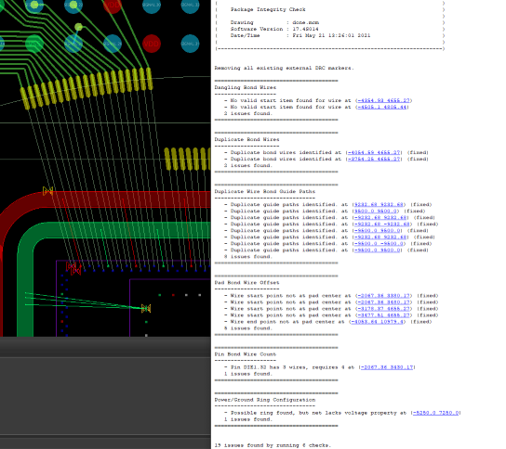

打開日誌檔 (log file),查看每個檢查中的錯誤資訊: |

|---|

修復與打線接合相關的封裝設計完整性問題

這些問題有多種解決方法。下面的例子中使用了一些我們推薦的方法:

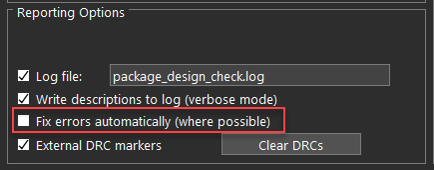

方法 1:自動修復錯誤

最好且最簡單的方法之一是讓應用程式自動修復錯誤。在 Package Design Integrity Checks 使用者介面中,在 Reporting Options 部分啟用 Fix errors automatically 選項 (在可能的情況下),然後點擊 OK,自動運行檢查和修復錯誤。

透過該選項可以快速有效地清除大多數關於打線接合的設計問題。

接下來,讓我們看看如何手動解決其中一些問題。

方法 2:修復打線的接合

在本例中,一些引線和相關的引腳位於不同的網路上。如果 die 有發生 ECO 和連通性變化,而這些變化沒有通知到設計的其他部分,就會出現這種問題。要移除這些 DRC,請選擇 Logic ─ Push Connectivity,將連通性從 die 的引腳傳播到設計的其他部分。

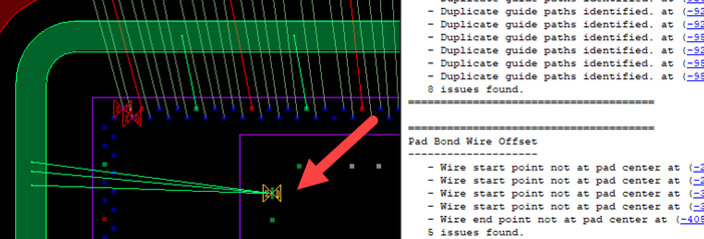

方法 3:修復引腳連接線數量

本例有一個 VSS 引腳,需要連接到四根連接線,以達到低電感值。我們可以透過設置引腳上的 WIRE_COUNT 屬性來指定連接線的數量要求。如下圖所示,只有三根連接線連接到 VSS 引腳上,該引腳由指標標記。

必須在這個引腳上再連接一條連接線才能解決這個問題。要添加一條額外的連接線,請使用 Route ─ Wire Bond ─ Add 命令。

方法 4:修復電源 / 接地環的配置

本例中的另一個問題是沒有為 VDD 網路分配正確的電壓值。要修復這個錯誤,請使用 Logic ─ Identify DC Nets 命令,為 VDD 網設置電壓值。

驗證與打線接合相關的封裝設計完整性問題

在修復所有的 DRC 後,再次運行封裝設計完整性檢查,以驗證所有的問題都已解決。在運行檢查之前,確保 Fix errors automatically 選項已被禁用。如下圖所示,所有的 DRC 都已修復,並且在日誌檔中沒有報告任何問題。

Allegro Package Designer Plus 具有內置的自動化功能,能夠分析和快速解決與具體打線接合相關的設計問題。運行封裝完整性檢查有助於設計師在前期修復大量的製造問題,如果到設計週期的後期階段才發現這些問題,修復的代價將十分昂貴。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」