By Cadence

DDR 佈線技術的重要性

在如今的印刷電路板設計中,DDR 記憶體非常普遍。許多設計都會用到 DDR 記憶體配置的不同版本,這需要在佈局中使用特定的佈線模式。DDR 的名稱來源於其能夠在每個時鐘週期內發送和接收兩次信號,是原先的單資料速率 (SDR) 記憶體速率的兩倍。由於速率增加了一倍,必須在佈設 DDR 記憶體的走線時保持更嚴格的參數,以滿足性能規範。

記憶體電路設計的關鍵在於滿足其時序規範。每個信號都有時間要求,以便於對應的時鐘信號在上升沿和下降沿對其採樣。由於資料速率在 DDR 記憶體的每次新反覆運算中得到提高,時序餘裕將變得更窄。這裡就需要精確的佈線模式來滿足時序要求。

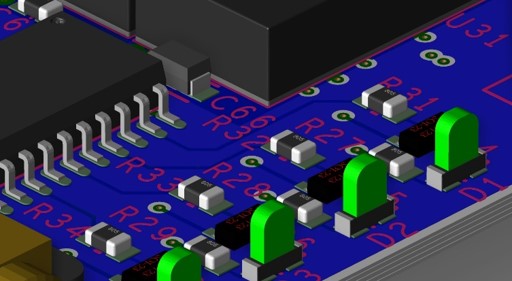

當為匹配長度而調整 DDR 佈線時,像這樣的蛇形佈線方式非常重要。

走線佈設

在對 DDR 進行佈線之前,我們仍然需要在佈局中遵循高速設計的基本原則。這些原則包括放置器件以重建電路圖上規定的信號路徑,以及將高速敏感電路與其他可能造成干擾的電路保持隔離。我們還需要在佈局中為DDR佈線通道和引腳出線留出足夠的空間。同時,需要將存儲晶片放在一起,並從最低位置的資料位元晶片開始,到最高位置的資料位元晶片結束,依次進行定位。

在設計 DDR 時需要注意的另一個佈局方面是設計供電網路。參考電壓在記憶體佈線的信號完整性方面起到非常關鍵的作用。參考電壓有誤會導致錯誤觸發信號,因此需要進行適當濾波以保持其指定的電平。這意味著使用旁路電容器來穩定電源網路,這將在佈局中佔據其他空間。

DDR 電路的佈線考慮因素

如前文所說,DDR 電路的關鍵點在於時序。這意味著時鐘線將決定存儲晶片中資料線的輸入時序和輸出時序。由於無法對電信號進行加速,因此控制時序的唯一方法是延長走線,以延遲時鐘信號的到達。這是透過在佈設走線時增加蛇形佈設方式來實現的。透過調整時鐘信號的到達時間,我們可以對資料線作出類似的調整,從而每位元資料都可以在下一時鐘週期之前到達並實現穩定。

在對 DDR 電路進行佈線時,通常使用兩種不同的佈線方法:T 型拓撲 和 Fly-by 拓撲:

T 型拓撲方法 |

|

以分支的方式將命令、位址和時鐘信號從控制器連接到記憶體模組,而資料線則直接連接。這種方法最初在 DDR2 中使用,但無法適用于具有更高信號速率的 DDR3 和 DDR4。分支對佈線來說是個挑戰,但具有能夠處理多晶粒元件的高電容負載的優勢。 |

|

Fly-by 拓撲佈線方法 |

|

更像是菊輪鍊拓撲方法,它以鏈的形式將命令、位址和時鐘信號從控制器連接到記憶體模組。同樣,資料線直接透過控制器和記憶體模組連接。該方法透過減少 T 型拓撲中走線的短截線數量來支援在更高頻率下進行操作,這也提高了其信號的完整性。Fly-by 拓撲的菊輪鍊結構也比 T 型拓撲的分支結構更易於進行佈線。 |

延伸閱讀 如何在 TopXp-SLA 快速自訂 Compliance Kit

同時對所有這些線路進行計時的關鍵是在佈線過程中調整和匹配走線的長度。只有滿足時序規範,才能按預期佈設 DDR 的走線。我們可以在資料手冊中找到這些規範要求,並應設置高速設計約束來滿足這些長度規範。

另一項重要因素是,在電路板的哪一層佈線也會影響佈線。在內層佈線 (帶狀線) 和在外層佈線 (微帶) 有著不同的性能特徵,會影響信號的速度。不能簡單地匹配內層和外層上走線的調整。同時,必須對這些走線進行調整,以考慮到不同的層特徵。此外,鑒於信號計時隨著每個新版本 DDR 的出現而變得越來越關鍵,需要在匹配的信號路徑總長中考慮到整個飛行時間 (TOF)。這意味著還要將內部封裝引線的尺寸納入到走線長度的計算中。

Cadence Allegro 等高階 PCB 設計工具可以讓複雜佈局變得輕鬆簡單。

未來就在眼前

我們已經看到了 DDR 記憶體的能力和 PCB 走線佈線支持在這些年裡穩步發展到目前的 DDR4 技術水準。現在,我們即將透過 DDR5 進入到記憶體發展的下個階段。隨著 DDR5 的基本速率達到 DDR4 的兩倍,佈線規範可能會更加嚴格。為了掌握這項先進技術,PCB 設計工程師需要佈局工具來應對即將遇到的新挑戰。設計工程師們將需要 DDR 佈線的流程規劃能力,以及內置於在 PCB 設計工具中的先進走線長度匹配和調整能力。

Cadence 公司的 PCB 設計工具可以為您提供在設計這些先進 DDR 佈線方法時所需的能力和性能。Allegro® PCB Designer 工具提供了約束驅動流程,可以簡化 DDR 佈線拓撲的設置,讓複雜佈局變得輕鬆簡單。

若您正在使用 Allegro PCB Designer,並希望升級到 17.4 最新版本,

維護期內 用戶,請點擊下方圖片 ↓↓

維護過期 用戶,請聯繫 映陽科技團隊

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」