By Eric Chen, Graser

【 PCB 設計同步分析 】系列專題將解密六大隱藏分析技巧,幫助 EE、Layout 人員在設計前期階段不需依靠 SI / PI 專家就能做初步的模擬分析,快速找出並排除常見訊號 / 電源問題,提升設計品質和效率。接下來會帶領大家一一解鎖 IR Drop、Coupling、Impedance、Crosstalk、Reflection、Return Path 分析技巧,歡迎共同探討。

高速設計已成為愈來愈多 PCB 設計人員關切的重點。在進行高速 PCB 設計時,每位工程師都應重視其訊號完整性,並且需時常考量其訊號電路的回流路徑,因為不良的回流路徑容易導致雜訊耦合等訊號完整性問題。 如果電流必須經過很長的路徑才能返回,訊號路徑的電感迴路會增加。當系統中的電感迴路越大,這些訊號愈有可能吸收來自系統中任何其他 Net 的雜訊。

一般回流路徑不連續問題常是由於缺少接地過孔 Via、接地層中的間隙、缺少去耦電容,或是使用錯誤 Net 所引起的。而當你的 PCB 設計愈趨複雜,要快速找出這些問題難度也愈高。

本篇將透過設計實例詳解如何使用 Allegro IDA (In-Design Analysis, 設計同步分析) 的 Return Path 分析功能,在 PCB 設計過程中進行回流路徑分析,幫助工程師快速找出那些高速訊號的回流路徑是否適當,以確保 Layout 的品質並且減少產品量產後因訊號不穩而需要召回的重大損失,實現設計一次性成功。

本文重點:

回流路徑釋義 |

|

Return Path 分析重要性 |

|

Return Path 分析實例詳解 |

|

Return Path 分析結果解析 |

|

番外篇 - 常見問題 |

何謂回流路徑 (Return Path) ?

電氣產品的運作需要有其訊號的迴路才能運行,就像下圖(一) 中電池的負極也要接那條藍線過去電燈才會亮。早期,我們可以看到電報系統是把「大地」當作訊號迴路的地平面,可以少佈另一條地線以減少昂貴成本。或若在現代生活中類似情況就是當車上要加裝燈泡時,我們可以把「車殼」視作訊號迴路的地,將燈泡負極直接接至車殼就會亮,就可以省掉多佈一條線的麻煩,且也不太需要考量到回流路徑問題。

不過若當要接上的是行車電腦、CAN (車載網路系統) 甚或是 ADAS (先進駕駛輔助系統) 上的各種感應或處理器,就不是直接接上、省掉導線這麼單純了,因較易涉及高頻 / 高速傳輸,會必須要注意其回流路徑的完整性。

圖一

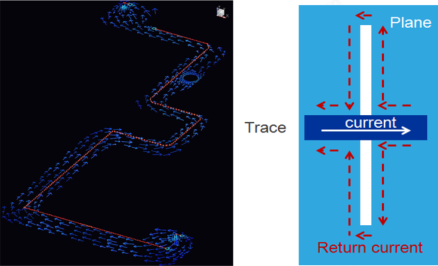

同樣的! 對 PCB 設計上來說,如果是低頻訊號其回流路徑會隨最低阻抗而返回,但隨著頻率拉高,電流需要以封閉回路回到源頭,因而會更考量最低電感的回流路徑,並且通常會對應在其佈線的上下層返回路徑如下左圖(二)示意,以避免如下右圖(二) 因內層切割而造成回流路徑迂迴的問題,所以高速訊號的回流路徑考量就更顯重要了。

圖二

為什麼需要 Return Path 分析?

如引言所述,考量高速訊號的回流路徑至關重要,因稍一不慎就會大大減弱電路功能。

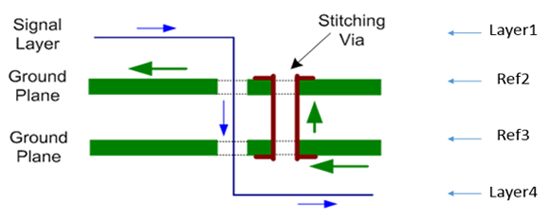

一般而言,因為標準 PCB 的 DRC 檢查只會檢查鼠線有沒接完和安全間距夠不夠這兩種狀況,所以像 Return Path 這樣的分析就較不易實現,往往需有經驗的老手開啟相關的圖層跟著看高速訊號走線的相鄰層來確保回流路徑,管控 Layout 品質。亦或對 Layout 訂立一些走線旁該怎麼加 Stitching Via 的規範,Stitching Via 的示意如下圖(三),至於差動訊號打 Via 後旁邊要拱幾個 Stitching Via,那又是另外的故事了!

圖三

甚或是最後不得已需添加縫補電容以填補那些跨不過壕溝 (Moat),而導致成本增加以完善回流路徑,如下圖(四) TI 規範中的例子。

圖四

圖片來源 : TI

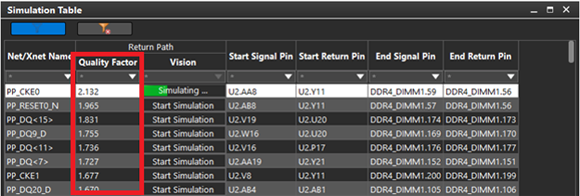

所以如果我們有個直觀的輔助分析工具會依照訊號的幾何結構分析回流路徑,並在不需 Models 的狀況下,計算出其電感的比值 RPQF (Return Path Quality Factor, 回流路徑品質係數) 如下圖五所示。

當 RPQF 值越 趨近於 1 ,則表示訊號佈線與回流路徑是越貼近的,越高則代表回流路徑越曲折繞越遠的路徑。

圖五

而且在執行分析完畢後可直接列出相關訊號的 RPQF 值如下圖六所示,讓我們能快速識別各個訊號的嚴重性,修正不理想的部分。

圖六

[小叮嚀] IDA (In-Design Analysis, 設計同步分析) 中另外的 Impedance 阻抗分析和 Coupling 耦合干擾分析,也是一樣可以在不需 Models 的情況下,照著檢查流程執行就可以很快實現各項 Layout 品質管控的快篩分析。

如何執行 Return Path 分析

現在 Allegro 中導入了 Sigrity 專業的模擬分析技術,將 IDA (In-Design Analysis, 設計同步分析) 帶入 PCB 設計流程之中,幫助 PCB 工程師在設計中同步進行分析,預先找出常見的回流路徑不連續問題,即時解決,快速確保訊號回流路徑的質量,使設計效率提升,不良機率減少。同樣重要的是 Return Path 檢查也是不需要 Models 並且只需簡單的流程,就可輕易實現!

下方影片先帶你快速瞭解 Allegro 的 Return Path 分析工作流程。

( 中文配音 ; 建議開啟音訊聆聽觀看 )

想進一步了解更多操作 Tips?

歡迎點擊下方圖片,下載 完整「 PCB 設計同步分析六大隱藏技巧 」電子書。

本電子書為 PDF 版本,全文 94 頁,將以實例逐一解鎖6大分析技巧,幫助您在設計前期階段不需依靠 SI / PI 專家就能做初步的模擬分析,快速找出並排除常見信號 / 電源問題,提升設計品質和效率。

番外篇 - 常見問題

什麼是 PCB 設計同步分析?

PCB 設計同步分析 (In-Design Analysis, IDA) 是將 Allegro® 設計介面與 Sigrity™ 分析引擎緊密結合而實現的全新功能。在 IDA 的工作流程中,Sigrity 分析引擎可提供快速的一級回應來對 PCB 設計工程師的工作進行指導。

IDA 功能與 Sigrity 工具中的模擬分析功能有什麼區別?在模擬精準度與速度方面哪個更有優勢?

相較於 IDA 功能,Sigrity 工具為 SI / PI 工程師提供了更多高階設置選項,提供最精確的分析結果。因此,根據模擬分析的設置不同,為了確保模擬精度,可能需要更長的時間來呈現分析結果。設計團隊可以根據具體情況進行不同工具的搭配和選擇。

如何使用 IDA 設計同步分析功能?

IDA 設計同步分析功能整合在 Cadence 最新發佈的 Sigrity™ Aurora 工具中,該工具為佈局前、設計中、以及佈局後的 PCB 設計提供設計同步訊號和電源完整性分析。整合 Allegro 的 PCB 編輯和佈線技術,Sigrity Aurora 用戶能夠在設計週期的早期,透過假設分析,設置更精確的設計約束 (constraints)、減少設計反覆運算。想了解更多資訊,歡迎造訪 Sigrity Aurora 。