By Eric Chen, Graser

【 PCB 設計同步分析 】系列專題將解密六大隱藏分析技巧,幫助 EE、Layout 人員在設計前期階段不需依靠 SI / PI 專家就能做初步的模擬分析,快速找出並排除常見訊號 / 電源問題,提升設計品質和效率。接下來會帶領大家一一解鎖 IR Drop、Coupling、Impedance、Crosstalk、Reflection、Return Path 分析技巧,歡迎共同探討。

以往 PCB 設計團隊在考量佈線品質兩大基本議題 Coupling 耦合干擾和 Impedance 阻抗時,因為沒有適當的工具和簡易的流程,都得在佈線後請 SI 人員作分析,但依其分析結果,PCB 設計人員卻又難以明確知道各問題的位置而即時進行適當調整,以符合訊號特性和品質的需求。

第二篇將與大家分享如何使用 Allegro 的 Coupling 分析功能,在 PCB 設計過程中預先進行訊號耦合分析,幫助 Layout 工程師快速找出可能發生耦合干擾的佈線問題,並能立即排除。

什麼是 Coupling?

在現實生活中,我們居住的環境充斥著各種噪聲,不管是樓下街道的喇叭聲、隔壁鄰居的電視聲,甚是在電話或對講機中偶而還會聽到別人的對話。當這些雜音影響到我們真正想聽的內容時,就會形成所謂的干擾。所以現在市面上有雙層的氣密窗,或是有強調主動降噪功能的耳機出現,就是希望能隔絕這些雜音,讓您耳根子能多點清淨或是只留下您想聽的美妙樂音。

同樣的! 對 PCB 設計上來說,在訊號傳輸上隨著佈線越密越近,訊號運作時會發生耦合而干擾旁邊(左右還有上下層間)的訊號,可能引起誤判而造成產品發生問題。

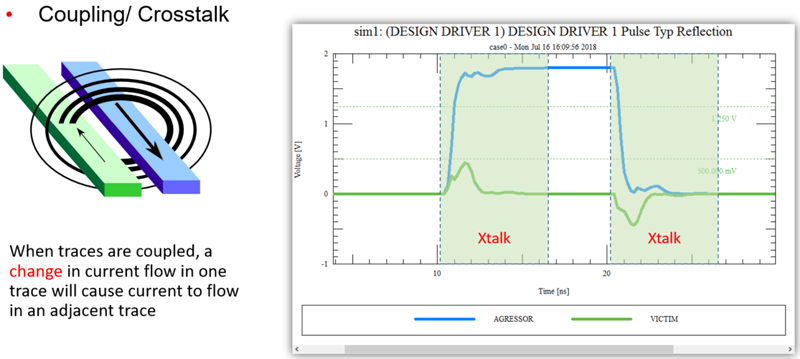

以下例子中傳輸訊號的傳輸線,稱之為 aggressor line (攻擊走線) 或 active line (動態線),會將一部份的訊號傳到無訊號的傳輸線上,稱為 victim line (受害走線) 或 quite line (靜態線) 而造成問題。

圖一

為什麼需要 Coupling 分析?

一般在設計 PCB 時,為避免 Coupling 或 Crosstalk 的狀況發生,有些公司會有 3W 三倍線寬這樣的規範,所以可能會在 Constraint Manager 中設定 Spacing 的間距值,或少數人會利用 Parallelism 設定可併行的間距與允許長度的搭配檢查值。這兩種的好處是可以不須套用 Models,但缺點是準確度不足。

如以下左圖的情況,當介質層很厚時,3W 的三倍線寬下雖然間距值夠了,但真的不會干擾嗎? 再者,即使是用 Parallelism 的間距 / 允許長度檢查,也可能會有不能跨層檢查相鄰層干擾等等的問題。

圖二

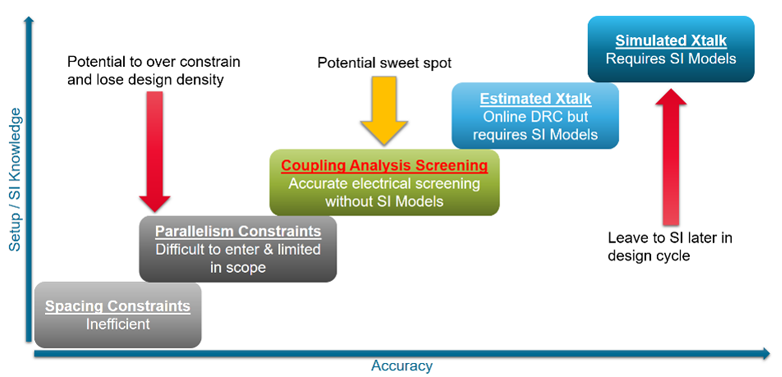

這就是如下圖(三)在各種干擾檢查準確比較中,左側所示的兩種 Constraints 方式:Spacing 和 Parallelism。 另外,若是要更準確就是如下圖(三)右側兩種方式: Estimated Xtalk 和 Simulated Xtalk,但這就需牽扯到零件要掛上 Models 或是要拜託 SI team 執行相關分析,因而需要更多的設定時間和經驗及資源才能實現。

圖三

所以 IDA 新流程中的 Coupling 分析檢查其特點為~不需要 Models 又可做夠精準的快速分析,簡單來說就是 -- 「Model不用、經驗不拘」。

現在您只要依照後面的檢查步驟,就有機會在 Layout 工具中實現耦合干擾快篩分析的目的,而不需擔心是否有 Models 或是否還要拜託誰才能檢查,以提升 Layout 的品質並且減少產品量產後因訊號不穩而需要召回的重大損失。

PS. IDA 中的另外一項 Impedance 阻抗分析也是一樣「Model不用、經驗不拘」照著檢查流程執行就可以很快實現佈線阻抗的快篩分析,我們將在 下一篇 : Impedance 阻抗分析技巧 分享更多細節,請持續關注【 PCB 設計同步分析 】系列專題。

如何執行 Coupling 耦合干擾分析

現在 Allegro 中導入了 Sigrity 專業的模擬分析技術,將 IDA (In-Design Analysis, 設計同步分析) 帶入 PCB 設計流程之中,幫助 PCB 設計團隊預先且即時分析訊號耦合問題,並修正不理想的部分,使設計效率提升,不良機率減少。下方影片將帶你快速瞭解 Allegro 的 Coupling 分析工作流程。

( 中文配音 ; 建議開啟音訊聆聽觀看 )

想進一步了解更多操作 Tips?

歡迎點擊下方圖片,下載 完整「 PCB 設計同步分析六大隱藏技巧 」電子書。

本電子書為 PDF 版本,全文 94 頁,將以實例逐一解鎖6大分析技巧,幫助您在設計前期階段不需依靠 SI / PI 專家就能做初步的模擬分析,快速找出並排除常見信號 / 電源問題,提升設計品質和效率。

※ 下一篇文章預告:Impedance 分析技巧