By Paul McLellan, Cadence

在前不久結束的 DesignCon 上,Cadence 及其客戶 IBM 就 32 GT/s 及以上的高級 IBIS-AMI 技術 做出了演講教程。Cadence 專家 Paul 親臨現場,為大家帶來第一手講義筆記~

IBIS-AMI 技術讓我想到了一個很好的類比:降噪耳機。如果我們想把音樂從智慧手機(發射器)傳輸到大腦(接收器)而不被噪音干擾,降噪耳機是我們的不二選擇。在播放音樂時,降噪耳機會對周圍的環境聲音進行採樣並輸入適量的負片來抑制背景雜訊。透過計算環境雜訊在到達耳膜時對聲音的影響,傳輸訊號會被調整以進行補償。

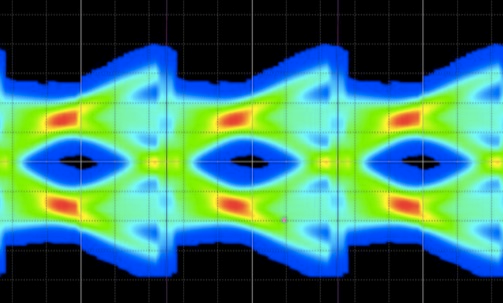

與降噪耳機相比,SerDes 發射器和接收器的工作原理更為複雜,但有一點是相同的:計算出通道會增加什麼失真,然後在發射器上進行補償。還有一系列額外的問題需要在接收器進行處理,這相當於在大腦中進行音訊處理。如下方眼圖,接收器有兩大工作需要完成:一方面確保有正確的電壓水準以區分 0 和 1,另一方面確保時序位置位於眼圖的中心。由於以上兩方面是移動變化的,因此我們需要自我調整均衡,而不是在設計時固定所有參數。

IBIS 和 AMI

20 多年以來,IBIS 都是通道建模標準,AMI 則是演算法建模介面。Cadence 參與了這兩個規範的制定,因此由 Cadence 的 Ken Willis、Kumar Keshavan、Mehdi Mechaik 和 Ambrish Varma,以及 IBM 的 Greg Edlund 來對此做出演講教程再合適不過。

該教程分為幾個部分,由不同專家介紹不同領域:

通道模擬基礎 |

|

均衡 |

|

時鐘資料恢復 |

|

自我調整均衡 |

|

抖動 |

演講一開始描述了使用傳統方法的動機,即使用電路模擬器。這種方法在平行介面時代是可行的,因為平行介面速度較慢且不需要運行很多位元來驗證是否可以工作。而今,我們使用 IBIS/AMI 和通道模擬:

多千兆串列鏈路需要通過大量的資料流量才能獲得可靠的眼圖 |

|

多千兆串列鏈路需要通過大量的資料流量來提供足夠的樣本以精確預測 BER(誤碼率) |

|

多千兆 SerDes 設備通常使用自我調整均衡,這需要通過大量的資料流量才能穩定和鎖定(可能需要數十萬位元,這就是為何電路模擬不符合當今要求) |

|

在 10 年的時間裡,資料傳輸速率從 2.5 Gbps 提高到了 32Gbps,使得一切更加複雜,未來的設計目標是 400Gbps 到 1Tbps(Cadence 已有 112G 的 SerDes 正常工作) |

因此,為了準確地模擬多千兆串列鏈路,我們需要使用快速準確的模擬模型來對非常大的位流進行模擬。在使用自我調整均衡時,由於在接收器鎖定前無法獲取有用資訊(例如眼睛是否睜開),我們需要捨棄大量模擬中的第一部分。

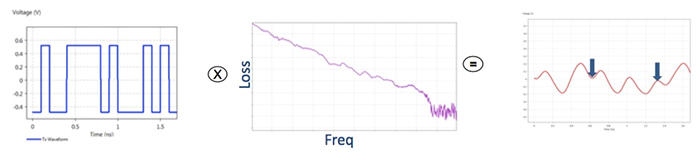

均衡

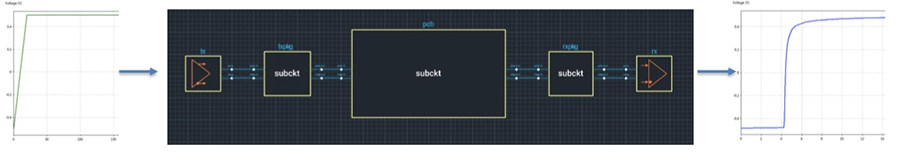

上圖顯示了為何需要均衡。左側是要傳輸的串列資料,中間是通道的頻率回應(高頻衰減很多,但並非簡單的線性回應),右側則是到達接收器的信號。可以看到存在大量失真且資料難以恢復(例如,左邊的黑色箭頭是 0,右邊的是 1,但是 1 的電壓低於 0 的電壓)。儘管傳輸是自同步的,但是從失真的波形中也很難將時鐘恢復。

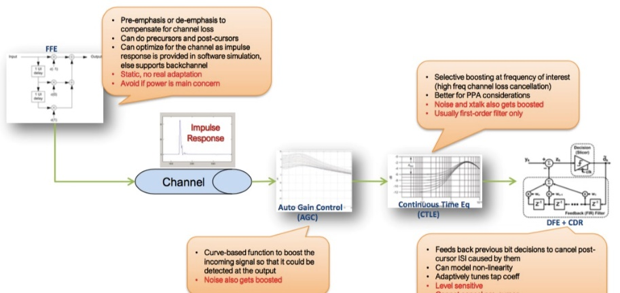

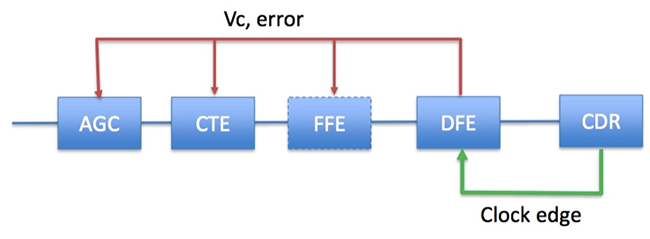

解決方案則是增加均衡。按順序,從發射器到接收器的均衡鏈依次為:

FFE 是前饋等化器,透過在發射器上增加預加重或去加重來補償通道 |

|

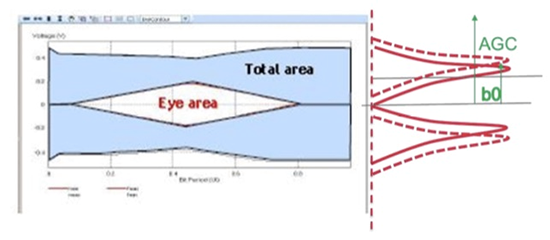

AGC 是自動增益控制,透過在接收器增強輸入信號(也同時增強雜訊),使下一階段 AGC 以輸入信號為中心 |

|

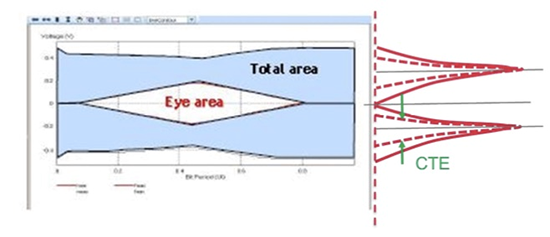

CTE 或 CTLE 是連續時間線性等化器,它衰減低頻信號分量,並在奈奎斯特頻率附近放大信號分量 |

|

DFE 和 CDR 是判決回饋均衡和時鐘資料恢復。這是最後處理訊號以恢復資料值流和時鐘的部分。回饋方面是,每隔幾個(使用者控制的)時鐘 ticks,使用中的參數就會根據之前的決策進行更新。隨著時間的推移(32G 的訊號不會以正好 32G 的速度運行),電壓(用來決定給定電壓是 0 還是 1 的值)將發生變化。DFE 和 CDR 使訊號方差保持在可控範圍內(DFE 用於訊號電平鑒別,CDR 用於檢測始終邊緣的分佈)。 |

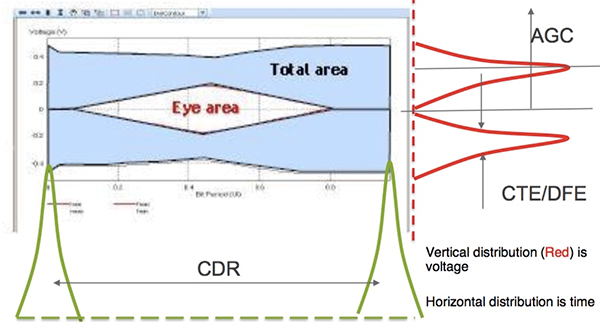

上圖顯示了目標。藍色陰影區域顯示訊號的去向。中間的白色眼睛是睜開的,意味著 DFE 工作良好(在垂直電壓方向上不讓訊號進入眼睛),同時 CDR 也工作良好(在水準時間方向上不讓訊號進入眼睛)。如果眼睛是睜開的,那麼資料值和時鐘就可以恢復,整個 SerDes 傳輸工作正常。一些較新的標準,如 DDR4 和即將發佈的 DDR5,定義了眼睛內必須始終保持清晰以滿足標準的區域。

發射器均衡

既然不能使用電路模擬,那麼我們需要做的第一件事就是……電路模擬。我們需要在設置的輸入(發射器輸出階段、通道、接收器輸入階段)上設置一個步驟函數,並測量響應。幾乎令人驚訝的是,單次模擬就包含了測量通道引入的失真所需的全部資訊。因此,就像降噪耳機一樣,我們可以在發射器中進行補償。上圖為電路模擬。

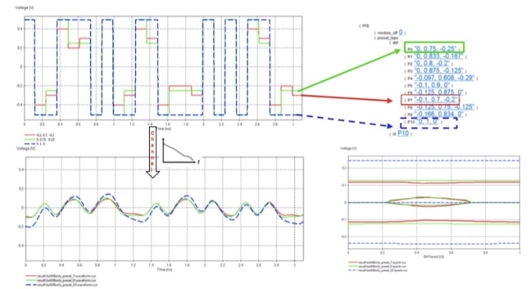

FFE 由被放入 AMI 模型的抽頭係數和預設值組成,以確保良好的訊號通過通道。上圖顯示了頂部的輸入訊號和底部的接收器(在完成所有接收器均衡之前)的值。藍色表示無均衡化的效果,綠色和紅色表示經過兩個抽頭值的效果。

接收器均衡

接收器的第一階段就是 AGC(自動增益控制),它將波形電壓集中起來為下一個均衡階段做準備。如上圖所示。

CTE(或 CTLE)用於「擠壓」0 和 1 的電壓分佈以保持眼睛睜開,由於其功耗低於 DFE,因此使用的標準更老、速度更慢。早期的 USB、MIPI 和其他版本只要在接收器上使用 CTE 即可;而更高的頻寬則要求 DFE。

DFE 和 CDR 共同工作。CDR 恢復時鐘,而在 DFE 期間則需要恢復的時鐘來獲取資料並定期調整均衡。另一方面,CDR 需要 DFE 清理的訊號來恢復時鐘。這種協同工作的方式,是接收器「鎖定」並恢復良好的時鐘和資料、睜開眼睛之前,需要花費數萬或數十萬位的原因之一。

CDR 必須定位採樣點,即波形的「中心」。這是自我調整均衡的基本出發點。它既要承受一定的抖動,又要在輸入訊號漂移時消除低頻抖動。CDR 有兩種類型,稱為 bang-bang 和 Müller。CDR 識別眼睛中心、過濾掉不相關的(高頻)抖動、拒絕低頻抖動(從長遠來看移動時鐘視窗)、在大量樣本(如 16 或 48)中 CDR判斷大多數樣本是否為早期或晚期(時鐘轉換在視窗中過早或過遲),然後縮放以進行調整。這以前是用(線性)類比電路完成的,而今全是數位電路。

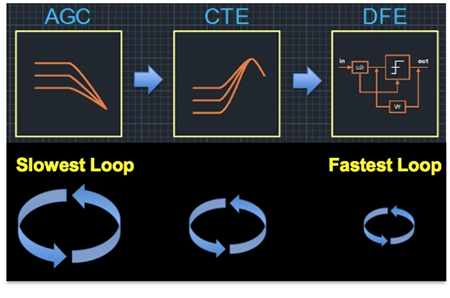

關鍵的權衡在於眼睛睜開和抖動容忍之間。如果調整的很快,那麼就會有更大的容忍度,代價則是眼睛變小。較慢的調整可以得到更大的眼睛,然而抖動的容忍度則會下降。

自我調整均衡鏈對通道損耗、溫度、半導體工藝極值和電壓進行補償。但是不對串擾、高頻電源雜訊和 EMI 進行補償。每個等化器都以它自己的速率對每 N 個位進行自我調整處理,當等化器最靠近封裝和 AGC 時變得最慢;當等化器最靠近鎖存器和 DFE 時也變得最慢。

訓練

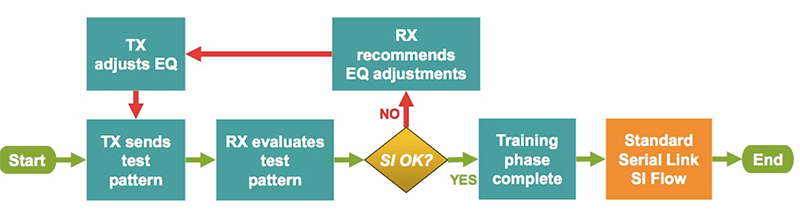

一個顯而易見的問題是如何初始化這些等化器參數。在此,AMI / IBIS 與從接收器到發射器的反向通道一起使用(實際上並不存在),以關閉發射器和接收器之間的迴圈。

上文提到等化器適用於工藝的 PVT 極值。但是實際上,這些參數並不存在於模型中。有一種假設是,如果某種適應性適用於其他所有事物,那麼它也可以用於工藝極值,但這可能有點牽強而需要實際驗證。

延伸閱讀

本文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」