2018 年將被銘記為 Sigrity 的 3D 年,Cadence® 推出了新的 Sigrity 3D Workbench 技術,為 Sigrity PowerSI® 3DEM 提取選項(3DEM)的一部分。該技術可幫助用戶導入機械結構,例如電纜和連接器,並與 PCB 合併,從而可以將從板到連接器的關鍵 3D 結構予以建模並優化。在 Cadence Allegro® 整合環境中,PCB 設計團隊能夠使用 Sigrity 工具來優化 PCB、IC 封裝和連接器的高速互連,同時在 Allegro 中自動實現 PCB 互連優化,而無需重新繪製。與其他 3D 工具相比,3D Workbench 可提供更高效、出錯率更低的解決方案,大幅縮短設計-模擬週期的同時降低設計失誤風險。

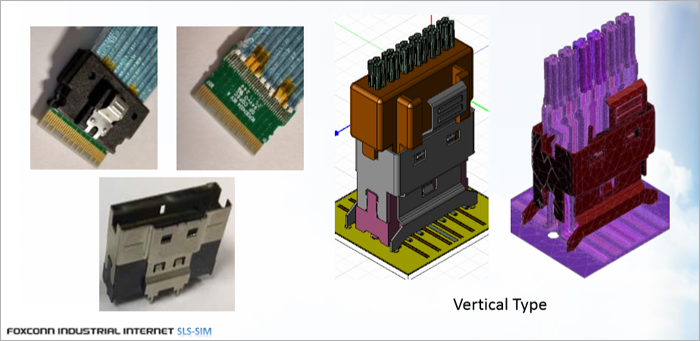

Cadence 全新 3D Workbench 技術也在客戶中得到了正向反饋。富士康工業互聯網 (FII) 在今年 CDNLive 用戶大會上,針對 PCB 主板和用於 PCI-e Gen4 或 SAS Gen4 的 SFF-8654 高速連接器,使用新的 3D Workbench 技術進行性能優化及其結果演示。

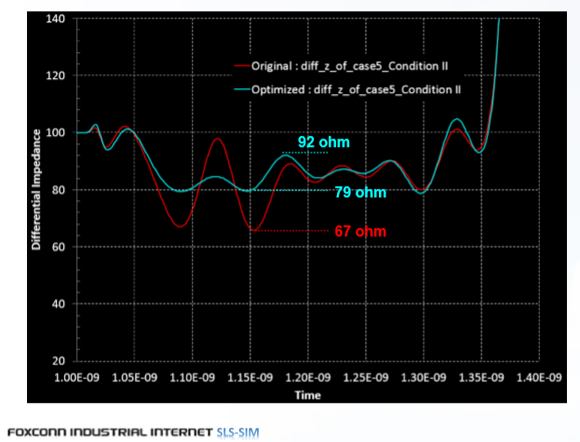

在富士康工業互聯網的演示內容中,將 Sigrity 3D Workbench 和其他 3D 工具進行比較,包含模擬流程、自適應網格元素和迭代數量,以及幾乎顯示相同的 S 參數精準度分析結果。確認 3D Workbench 的性能和準確性之後,在 3D Workbench 中針對不同的情況和條件進行 S 參數和 FEXT&NEXT 模擬。最後,執行時域 TDR 分析和模擬以完成優化過程,從而使整體連接器 TDR 差分阻抗滿足 85W±10% 的要求。