5G 是移动通信发展的下一个重要里程碑,目标是到 2020 年实现更大的流量 (10,000 倍) 、更高的容量 (1,000 倍) 、更低的延迟 (<1 毫秒) 和更低的能耗 (降低 10%) 。而创新的高频电子元件为下一代通信系统以及未来无线连接生态系统奠定基础。为实现随时随地高速传输数据,系统架构日益复杂,对器件级设计带来巨大挑战。

Cadence® AWR® Design Environment 提供完善的系统、电路与电磁协同仿真能力,结合 NI 的简化测试解决方案,协助 RF 与微波工程师有效应对新一代射频设计需求。

本白皮书为 PDF 版本,共 14 页,将深入探讨如何使用 AWR Design Environment 平台 (包括 AWR Microwave Office、AWR VSS 和 AWR AXIEM 软件) 进行电路、系统与电磁协同仿真,并结合 NI PXI、VST 和 LabVIEW 的测量平台,有效优化宽带 ET 功率放大器于不同频段和应用情境下的设计效能,显著加快产品开发速度。

本书重点

5G/LTE 包络跟踪功率放大器的产品设计流程 |

|

LTE 功率放大器设计挑战 |

|

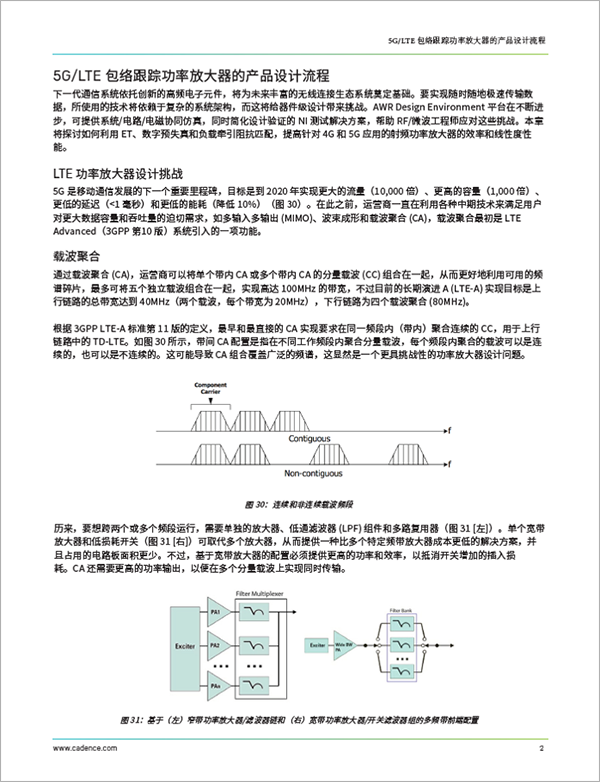

载波聚合 |

|

OFDMA、SC-FDMA、PAPR 和效率 |

|

负载牵引和匹配网络设计 |

|

通过系统仿真确定功率放大器的要求 |

|

使用 ET 和 DPD 提高效率和线性度 |

|

实际案例:使用 DPD 的 ET 功率放大器 |

|

用于 ETPA 开发的测试解决方案 |

|

使用 PXI、VST 和 AWR Design Environment 的 ET 结果 |

中文版授权转载出处 (Graser 协同校阅)

长按识别 QRcode,关注「Cadence 楷登 PCB 及封装资源中心」