本文作者:Cadence AWR Team,首發於 High Frequency Electronics 網站專欄

隨著積體電路 (IC) 技術不斷發展,該領域的設計師要不斷適應在性能、成本、效益和風險等因素驅動下不斷變化的製造技術。如今,和固態技術打交道的功率放大器設計師必須靈活使用各種工藝,包括砷化鎵 (GaA)、氮化鎵 (GaN) 和碳化矽 (SiC) PHEMT、射頻互補金屬氧化物半導體 (RF CMOS) 和砷化鎵或矽鍺 (SiGe) 異質結雙極電晶體 (HBT) 等。

同樣,要應對不同的設計挑戰,需要使用不同的放大器類別和 / 或拓撲結構,如 AB 類放大器、達林頓多晶體管配置 (Darlington multi-transistor configuration)、開關模式功率放大器和數位預失真。從一種技術切換到另一種技術,意味著某些技能和知識是可以轉移的。這些技能中最基本的是有效使用電子設計自動化 (EDA) 工具來設計 MMIC。更具體地說,這是一種戰略、設計流程或指南,闡述了如何從需求和工藝設計套件 (PDK) 入手,直到處理更複雜的需求。

本文將從系統的角度研究砷化鎵 (GaA) 偽形態高電子遷移率電晶體 (pHEMT) 功率放大器 (PA) 的設計方法。該設計方法使用了 Cadence AWR Microwave Office 電路設計軟體實現了一個簡單的 A 類砷化鎵 pHEMT 單片微波積體電路 (MMIC) 功率放大器設計,重點關注大多數功率放大器設計專案的設計流程及其基本特徵。將首先介紹設計收斂的概念,然後闡述參數化設計,要理解 PA 設計過程中的每一步,這些是需要瞭解的關鍵概念。

一般的設計流程

設計流程有時看起來比較混亂,但在從概念到完成的整個設計過程中,是有邏輯和順序可言的。設計流程可以用幾種不同的方式來看待,也許這就是造成混亂的原因。如果把設計流程看成是一系列重複或迭代步驟,直到模擬性能趨向於符合所需的要求,就很容易忽略設計的基本結構,而這種結構使其成為一種可重複、可靠的方法。自上而下的設計流程是非常理想的,因為這實現了可預測性。透過將設計參數與整體性能聯繫起來,工程設計團隊可以藉由明確定義的因果關係深入探索設計的各個元素。

另一方面,自下而上的設計在一定程度上保證了每個設計項目都能實現工程團隊所設想的必要功能。透過從微觀到宏觀、從網表到行為、從佈線圖到示意圖等角度證明每個零件都做到了這一點,工程團隊就可以證明設計符合預期的要求——「設計收斂」。這就是工程設計流程的兩個重要標誌:參數化設計和設計收斂,是一種非常簡潔的設計流程處理方法,在微波 [1-4,6] 和類比混合訊號 [5] 設計方面,已經對此進行了多次闡述。

應用於砷化鎵 MMIC 功率放大器的設計流程

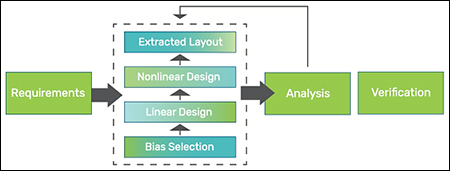

對於典型的砷化鎵功率放大器的設計,其設計流程如圖 1 所示。考慮到所需的性能,設計步驟 (虛線框) 要更為詳細;隨著探索更複雜的現象,設計團隊需要努力定義越來越多的功率放大器行為。在設計的每個子步驟中收集到的對電路的詳細瞭解,最終可以確保完整描述功率放大器的複雜性能——這在本質上是一種「循序漸進」的方法。

圖 1:帶有反覆分析的通用增量設計流程。

第一次迭代可能只是選擇偏置點,但這一步可能也很複雜,如負載牽引或熱方面的考慮因素。第二次迭代的重點是輸入和輸出網路設計方面的線性性能和穩定性。同樣,這一步也不能掉以輕心,因為一個大型的線性零件陣列必須採用多支路饋電,不僅要為源和負載阻抗提供良好的匹配,還要為陣列中的所有單個場效應電晶體 (FET) 提供相位。線性設計之後是非線性性能,設計在這個階段真正切入正題;在保證線性增益和穩定性的同時,還要詳細檢查飽和度和效率。

必須做出權衡,然後在製作佈局時進行微調,之後在設計的第四步 (也是最後一步) 中提取,輸入到模擬中。設計完成之後緊接著進行分析,以確保假設是合理的,並瞭解二階效應。此時的工作包括進行全面的電磁 (EM) 分析,以確保佈局符合標準和耦合最小化,並進行反覆運算電熱分析,保證通道溫度得到充分類比。最後一步是驗證,旨在透過設計規則檢查 (DRC) 確認設計可以投入生產,這是最後的機會,可以確保設計在流片之前符合性能、製造、測試和包裝的要求。

功率放大器設計示例

第 1 步:設計要求

我們來看一下 GaA PHEMT 功率放大器的設計流程,本示例研究了各種設計考慮因素的作用,並展示了參數化設計和設計收斂是如何體現的。在本例中,要設計的是一個由直流電源供電的 A 類放大器,規格匯總如下:在給定的線性天線輸出功率下,最大的功率附加效率 (PAE) Pant,從功率放大器的 P1dB 功率略微回退 ,帶有適度的 (單級) 增益 (G) 和一些天線不匹配。

第 2 步:偏置選擇

子步驟 2.1:電能耗散

為了實現這一設計,用戶可以透過一些簡單計算來分析偏置選擇。在第一個設計子步驟中,與所有步驟一樣,有必要清楚地說明要達到什麼樣的設計要求,確定哪些設計參數對於滿足設計要求來說是最重要的,然後證明為這些參數選定的參數值可以滿足要求。

如果不選擇適當的偏置點和相關的 FET 週邊電路,就沒有增益 (G),放大器可能不支持足夠的輸出功率 (Pant),而且可能遠遠達不到線性 (P1dB)。簡而言之,如果將 PAE 作為一項設計要求,並將 pHEMT 直流 Ids 和 Vds 視為設計參數,那麼第一步就可以從參數化設計的角度入手。

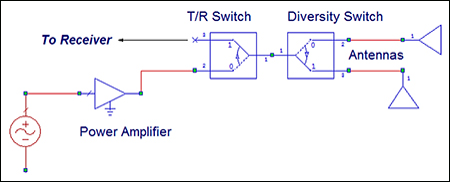

對於實際的功率放大器輸出功率,可能需要考慮設計中的其他元素。有時,功率放大器的設計要求並不是只針對功率放大器本身,而是針對系統,或是針對系統和功率放大器兩者。圖 2 是一個設計合理的從功率放大器到天線的系統,同時重點顯示了在將系統要求轉化為功率放大器要求時可能需要考慮的幾個額外元素。

隨著納入開關和考慮天線阻抗,天線上的功率或系統功率輸出與對功率放大器的功率要求聯繫了起來。

Pout = Pant + Lossswitches + Lossmatch + margin (1)

Lossswitches 是透過發射 - 接收 (TR) 開關和 / 或分集開關的損耗 (圖 2),Lossmatch 是天線上的不匹配,而 margin 是設計和回退的綜合餘量。雖然在電腦輔助設計 (CAD) 模擬的理想情況下,功率放大器將提供所模擬的全部功率;但在現實中,功率放大器出廠後,設備與設備或批次與批次之間的輸出功率 (Pout) 會出現差異,而用戶希望我們在餘量中考慮這一點。

圖 2: 系統圖:基於天線性能,影響功率放大器規格的元素

從 (1) 中,功率放大器內的電能耗散 (PDC) 可以根據 PAE 確定:

PDC = exp(Pout/10) * 1/PAE (2)

在無功負載的情況下,漏極-源極電壓和 VDC 大致相同——換句話說,在沒有漏極 (負載) 電阻的情況下,直流漏極偏置電壓完全降落在電晶體漏極源極上。

IQ = PDC/VDC = IQ(Vgs, Temp) (3)

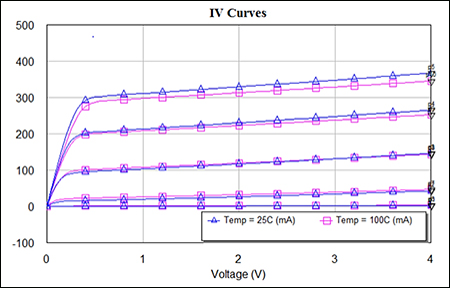

根據 IQ (靜態漏源電流)、裝置的 IV 曲線以及相應的柵極-源極電壓 (Vgs),在該電壓下,PHEMT 應被偏置為溫度的函數。FET 週邊電路的尺寸界定:選擇 Ids 作為 Vds 的函數,大約在 VDC 和通道溫度下 IV 特性曲線「膝蓋」之間的中點位置。對中點位置的選擇是由 A 類放大器的設計目標決定的,並取決於是否選擇 AB、B 等拓撲結構。這體現了第一個設計子步驟的基本方面。

整個子步驟可以透過 AWR Microwave Office 軟體快速高效地完成。可以使用兩個 IVCURVE 元素中的任何一個來設置直流 IV 掃描,以類比嵌套的直流掃描分析 (雙極管的電壓過電流或 FET 的電壓過電壓)。大多數得到廣泛支持的 MMIC 工藝包括具有直流偏置溫度的 FET 模型,因此可以透過調諧 / 掃描進一步探索 IV 曲線。經典的 FET IV 曲線圖體現了 IDS 與溫度的關係 (如圖 3 所示),也有助於查看電流梯度並判斷它是否是實質性的。

圖 3:環境溫度 (藍色,25℃) 和高溫 (紅色,100℃) 下的 IV 特徵。

子步驟 2.2:熱耗散

在實際開始小訊號設計之前,可以暫停並考慮熱影響,特別是考慮到方程式 (3) 中存在著溫度依賴性。像 GaA PHEMT 這樣的 FET 器件是多數載流子器件,其控制端由決定輸出端電流的電壓主導。對這一物理過程的熱敏感性源自多數載流子的濃度增加了,而這又被額外的散射機制所抵消,此類散射機制總體上表現為輸出電流隨工作溫度升高而減少。這是一個負反饋過程。圖 3 闡明了這兩種效應之間的平衡。在較低的電流下,溫度較高的器件在通道中有更多的載流子,由此產生的電流比室溫下的器件產生的電流要高。隨著自熱成為主導因素,溫度升高增加了散射,使載流子更難從源極穿越到漏極,從而導致電流減少。

在實踐中,pHEMT 的電流變化相對較小 [6],除了非常現實的可靠性考量之外,溫度在 pHEMT 設計中的影響比使用雙極結型電晶體 (BJT) 的 PA 電氣設計要小,因為在雙極結型電晶體中,熱失控是一個切實存在的問題。從設計流程的角度來看,由於偏置電路對溫度很敏感,而且相對於室溫和/或基板溫度,FET 通道中的溫度傾向於「牽引」偏置電路,在初始偏置設計步驟時將溫度考慮在內是一種謹慎的做法,但不一定有必要。

子步驟 2.3:負載牽引

在功率放大器的偏置選擇中,另一個考慮因素是負載牽引,即 FET 在非線性工作中有效輸出阻抗的轉變。這意味著,隨著輸入訊號功率的變化,FET 將在較低的功率下以線性方式工作,但隨著功率的改變,FET 會發生轉變。在現實中,在測量一個特定的性能參數時,負載阻抗會改變,這樣就可以有利地選擇呈現給 FET 的阻抗。另外,鑒於 FET 的運行方式具有某種程度的非線性,這種非線性是如何被負載阻抗改變的呢?這顯然是一個參數化的設計流程問題,因為某個指定的性能標準與設計參數 (FET 觀察到的負載) 有關。

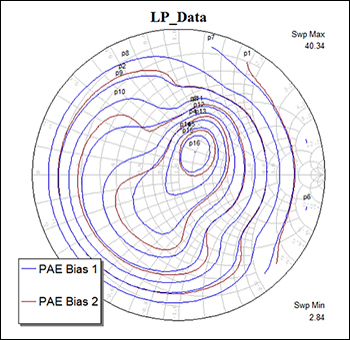

因此,當考慮到負載牽引時,僅僅根據負載牽引考慮因素而選擇偏置是不夠的,還必須說明哪些非線性輸出特性被哪個負載阻抗所「牽引」。出於這個原因,負載牽引資料通常以史密斯圓圖上的圓圈形式呈現。PAE 或飽和輸出功率是典型值,但二次或三次諧波消除也很重要。在更詳細的功率放大器設計方法中,如波形工程設計,整個 FET 模型基本上是 FET 的負載牽引資料,使用的是所需輸入訊號的近似值。由於這些原因,這一步可以視為步驟 3 線性設計的一部分,因為監測的性能標準是 IV 曲線以外的東西。

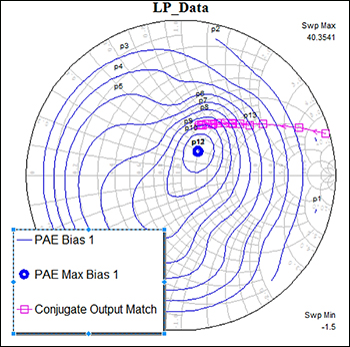

AWR Microwave Office 的負載牽引工具是一個很好的腳本,可以在設計中調用。圖 4 顯示了圖 3 中所用器件的負載牽引等值線——PAE 的等值線與兩個不同的偏置條件的比較。設計師可以根據直流耗散功率 (即不同的偏置條件) 和呈現給電晶體的不同 (負載) 阻抗 (即負載牽引等高線本身),檢查可用效率。從設計的角度來看,也許更重要的是同時使用類比的負載牽引能力和電晶體與柵極偏置的共軛小訊號輸出匹配 (圖 5) 。由於最大功率傳輸需要電晶體的共軛輸出匹配,負載牽引等高線對設計流程十分重要,因為最大功率傳輸和 PAE 的交叉部分有助於實現一個功能良好的功率放大器。有一點需要注意的是:由於這個功率放大器已經被指定為從 P1dB「回退」的模式下工作,小訊號 S22 可以用來代替測量值 (使用該測量值可以得出大訊號等值)。

圖 4: 使用 AWR Microwave Office 負載牽引腳本類比 PAE 負載牽引等高線,以比較帶有恒定漏極偏置的兩種不同的柵極偏置條件。

同樣,與熱方面的「迷你流程」一樣,如果花時間只對 FET 階段進行負載牽引分析,可以將其作為其餘步驟的設計收斂條件。當對輸出匹配網路的阻抗有了更好的理解,也可以在以後擴展該步驟,以查看非線性性能,並確認 FET 級的性能。

第 3 步:線性設計

在不過度簡化的情況下,下一步是調整參數,這些參數定義了呈現給 pHEMT 的輸入和輸出網路,進而先後獲得偏置和線性性能。換句話說,流程的參數化設計方面使用戶能夠調整 FET 觀察到的輸入和輸出阻抗,以便控制線性性能。在先進的流程中,這可能意味著基於功率放大器的基本頻率和諧波來設計輸入和 / 或輸出網路。設計收斂是另一個流程標準,要實現設計收斂,需維持子步驟 2.1 的性能 (基本上是維持實現 P 和 Pout 所需的直流偏壓) ,同時獲得所需的增益和匹配。

圖 5:類比的 PAE 負載牽引等高線與共軛 S22 匹配。

通常情況下,藉由獲得正確的偏壓和滿足輸出功率限制而實現的 pHEMT 週邊電路,其輸入和輸出阻抗接近 50Ω,但也許還不夠接近,所以可能仍然需要一定程度的阻抗匹配。對於大型 FET,輸入柵級-源級電容可能相當大 (圖 6) ,因此隨著工作頻率的提高,輸入阻抗將開始隨頻率變化而變化,輸入匹配變得更具挑戰性。

在實現輸入匹配時應注意穩定性因素,在這一步中,溫度考慮的優先順序最低。具體來說,如果 PA FET 柵極的直流偏置網路設計得當,帶有扼流圈和旁路電容,就有可能產生低頻共振,從而導致振盪的發生。因此,除了將增益 (G) 作為這一步的設計要求外,還應該考慮到線性穩定性指標,如 K 和 B1。在更高級的設計流程中,穩定性也會作為一個非線性設計目標被考慮在內 [8]。

儘管輸入匹配對於確保發射器鏈中的早期元件協調運行很重要,但功率放大器的重點是輸出端。首先,如果沒有正確設計輸出網路以獲得增益,我們得到的就不是一個放大器,更不可能是一個功率放大器。為了獲得最大的電壓擺幅,從而獲得最高的功率輸出,需要使用一個負載電感器,以便將電阻損失降到最低,電阻損失會限制從 FET 漏極測得的 Vdc 可用電壓。即:

Vd=Vdc-min(Vds(t))-IdsRe(ZL) (4)

或者說,漏極的可用電壓等於直流源電壓減去 Vds 最小值,即保持 FET 不超過“膝蓋”和保持電壓不因負載中任何實際阻抗成分而下降所需的最小 Vds。乍一看,答案是我們需要一個大號 MMIC 電感器;然而,大號 MMIC 電感器通常電阻較大,所以要做一個權衡。進行權衡時必須考慮功率放大器是徹底的單片式 (帶有片上負載電感器) 還是外接式。外接式片外電感器可能相當有吸引力,因為它具有更高的 Q 值和更低的損耗,但訊號到達片外設備帶來的額外寄生電容和電感會帶來進一步的穩定性問題。

前面在討論負載牽引時提到,良好的輸出匹配對於不超出 (1) 中規定的餘量也是至關重要的,因此應該透過負載牽引模擬或測量 [7] 來確定輸出匹配,從而確定實現最大功率傳輸所需的共軛匹配:

Zout = Z*d(5)

其中 Z*d 是 FET / 負載電路的阻抗的複共軛,

Zout 是 FET / 負載電路的輸出匹配網路的阻抗,並在其輸出端由所需負載 (通常為 50Ω) 終止。

隨著 Pout 變得越來越大,這一點變得愈發重要。功率放大器的作用是為天線提供功率,如果在功率放大器 FET 和代表功率放大器的引腳或連接器之間儲存或耗散功率,就無法實現這個目標。設計一個適當的匹配網路,將 FET 漏極處的「不完全等於 50Ω」變為引腳 / 連接器處的「盡可能接近 50Ω」,可能是從不達標變成超標的關鍵。

這一步的設計收斂應該確認直流偏置仍然為預期的 PAE 提供額定的直流功耗,並確認線性增益 (G) 以及任何輸入和輸出匹配標準 (分別以 VSWR 或 S11 / S22 表示) 已經實現。

在 AWR 軟體中實現這一點非常簡單,與設計小訊號放大器或無源電路沒有區別。創建電路圖,在幾個圖形上執行所需的測量值就可以了。要想加快後續步驟的進度,有一個小提示:可以按層級結構設置電路,模擬平臺位於最上層,特別是對於非線性模擬而言,但一定要使用理想元件,讓初始電路圖簡單易懂,並保留 MMIC PDK 螺旋電感器模型,直到拓撲結構更加明確。這往往會使關鍵的設計參數在早期更容易確定,因為不會由於寄生效應而混淆結果。

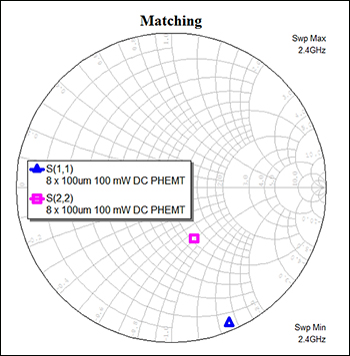

圖 6:PHEMT 的輸入和輸出阻抗與 50Ω 不匹配,而且電容值很高。

從圖 6 可以看出,電晶體的 S22 幾乎位於對應於 50Ω 的阻抗圓圈的實部。 (圖 5 也顯示了這個值位於史密斯圓圖的上半部分,作為共軛匹配) 。這使得共軛匹配似乎只需要增加一個等效的串聯電感,但在更高的頻率下,這樣做更難實現 (因為互連的長度將電感變成了傳輸線) ,而且功率輸出也會上升 (因為根據設計規則,需要使用更粗的線路來傳輸電流) 。通常情況下,這種操作會比較複雜,需要使用一些階梯式阻抗變壓器來實現阻抗的實部匹配,以及與任何虛部實現共軛匹配。對於這種設計,幾奈米的等效電感 (圖 7) 就已足夠,但如果是位於晶片上,或者用於封裝,如果考慮到提到的尺寸和電流處理的限制,這樣做不可行,那麼如何實現這一點就要取決於佈局。

圖 7:匹配的輸出阻抗,為此使用一個集總電感來提供電晶體 S22 的等效共軛阻抗。

回過頭來參考圖 5,注意最大功率傳輸的匹配並不對應於最佳 PAE 的匹配。當考慮到設計的非線性方面時,需要作出權衡,但在這一點上,我們已經通過完成小訊號設計標準 (即我們希望實現的匹配) 實現了小訊號的設計收斂。

第 4 步:非線性設計

第三次設計參數/收斂迭代側重於非線性性能、PAE 以及透過微調偏置和匹配得到的 P1dB。但與線性設計步驟一樣,為了實現設計收斂,已經獲得的參數不應受到干擾,所以必須在不犧牲增益、匹配和 (也許在這一步是最重要的) 穩定性的情況下優化非線性性能。以破壞設計穩定性的方式來提高 PAE 是很有吸引力的——畢竟,要想在相同的直流電源下獲得更多的功率,只需製造一個振盪器就大功告成了!

從設計流程的參數化設計要求的角度來看,在這一步中控制性能的設計參數似乎與上一步相同,只是我們使用非線性模擬器來觀察 PAE 和 P1dB (或其他一些非線性的衡量標準) 。其實非常適合在這一步中對輸入和輸出匹配網路的實際構成多加考慮,其中包括偏置線、接地以及片外和片內的鍵合線或 bump。通常情況下,我們會監測寄生源電感的界限,從而為佈線圖 (邊界焊盤的數量和位置) 和封裝 (鍵合線的數量和長度) 提供指導,其中不僅涉及到降低非線性性能標準,還要確保仍然滿足與前面的子步驟相關的要求。

在這一步中,重點是在輸入功率逐漸上升時,努力將線性輸出功率的壓縮點向外推,以及提高 PAE。要做到這一點 (繼而實現這一步的設計收斂) ,所採取的策略重點是最大限度地減少寄生效應和略微調整偏置條件。我們可能會很想改變 FET 週邊電路,但這樣做是有風險的,在涉及到負載牽引的情況下更是如此,因為我們可能已經根據對 FET 輸入和輸出阻抗的詳細瞭解對設計的線性部分進行了優化。如果 (3) 中的 IQ 可以回退,以提高 PAE 而不損害線性性能,那麼就可以用較低的電流製造一些熱餘量。

關於 FET 建模,應該強調一點:清楚而詳細地瞭解 FET 的非線性行為,瞭解正在使用的模型在多大程度上捕捉到了這些非線性行為,這一點至關重要。例如,如果目的是通過巧妙的阻抗匹配 (作為擴大 P1dB 的一種方式) 來儘量減少三階諧波的產生,那麼所使用的模型不僅應該能準確地通過 gm (基於電流的非線性) 或 Cgs/Cgd (基於電容的非線性) 的導數產生三階諧波,而且在負載阻抗不等於 50Ω 的情況下也要做到這一點。對模型的這種要求並非是微不足道的,相反,在沒有驗證模型是否具有這種能力的情況下,試圖類比和“設計出”這種行為是非常不明智的,只會浪費時間。

如果專案組織的模擬平臺樣式 (圖 8) 已經確定,AWR Microwave Office 非線性模擬可以與線性分析重複使用,只需更改模擬平臺上執行的測量——AWR 軟體中的埠 (乃至非線性源埠) 作為 S 參數終端,因此可以從圖表中獲得兩種用途。在 AWR Microwave Office 軟體中,埠元素既是線性終端又是子電路/層次元素。如果模擬平臺的底層電路圖在一開始包括片外或偏置相關的寄生效應,那麼在所有分析中重複使用底層電路圖是很重要的。此外,如果功率放大器是 C 級或更高的等級,設計師可以開始使用暫態分析,並且模擬平臺電路圖層面上的模擬設置保持不變。

圖 8. 專案開發的模擬平臺樣式,其中 (左) 線性分析和 (右) 非線性分析共用同一個子電路,以確保參數化設計和設計收斂標準的一致性。

對於本例而言,重要的非線性測量值是 PAE 以及增益壓縮 (圖 9) 。PAE 是需要進行優化的參數,但在本設計中引入的原始約束是讓功率放大器從 P1dB「回退」。這意味著,對於一些給定的輸出功率,功率放大器的實際工作點必須對應於一個輸出功率,即略低於放大器增益的壓縮點。

圖 9:電晶體的 PAE (%) 和輸出功率 (dBm):針對最大 PAE 而優化匹配與針對最大功率傳輸而共軛匹配。

如果該特定的 FET 尺寸和偏置與針對最大功率傳輸的共軛匹配一起使用,那麼功率放大器在較低的輸出功率下會壓縮,不能提供最佳的 PAE。圖 5 中的負載牽引等高線就表明了這一點,因為共軛 S22 匹配與該偏置點的負載牽引結果的交叉顯示,功率放大器將不會實現 PAE 最大值。該偏置點的負載牽引等高線清楚表明,這兩者不能同時實現。

在實踐中,更常見的情況是,功率放大器的設計要求電晶體要以犧牲 PAE 為代價實現共軛匹配。在這種情況下,負載牽引將是相對於最大功率傳輸,而不是相對於 PAE。這將產生一個最佳匹配,它不會對應於小訊號 S22,但會給出一個阻抗,「拉走」小訊號 S22。

第 5 步:提取 layout

完成電路設計後,最後的設計步驟是實際佈置功率放大器。如果在電路圖上沒有捕捉到互連,那麼參數化設計的要求就會有點喪失存在感,因此,微帶或共面波導元件應該盡可能擺放在電路圖上,這樣長度和寬度就可以與維持整體晶片的性能標準聯繫起來。不少 MMIC 設計 (包括功率放大器) 從來沒有順利通過產品開發的這個階段,原因很簡單:在設計過程的這個階段,在無休止的「移動一條線,運行電磁求解器,進行電路模擬....然後再來一次」的過程中,這種參數化設計的要求漸漸消失了。面對幾十個或上百個互連和一個不能實現設計收斂的提取layout圖,設計團隊必須儘早確定哪些互連控制著 MMIC 的關鍵性能。如果 MMIC 的 PDK 支援鍵合焊盤,那麼它們也應該被納入參數化設計階段。

在包含所有這些影響的名義模擬確認整體晶片性能標準得到滿足之後,設計收斂就完成了。小規模 (小於晶片規模) 的電磁分析可以在本地完成,以確認輸入和輸出匹配網路達到了所期望的性能,如公式 (5) 所定義的那樣。

在功率放大器設計流程的這一階段,AWR Microwave Office 軟體中的流程非常有説明。沿著通常要進行電路劃分的線路 (輸入匹配、FET 級和輸出匹配) 使用 EXTRACT 技術,用戶能夠快速確認佈線後的性能是否符合設計早期基於電路圖的估計。不要忘記把 PDK 的鍵合焊盤作為電路圖模擬和 EXTRACT 設計 (如果可能的話) 的一部分。

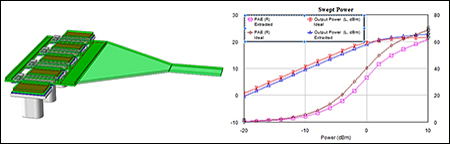

例如,圖 10 顯示了一個簡單的漏極多支路結構,用於從從本例中使用的 FET 的漏極結構過渡到 50um 厚 GaA 上的 50um 線路中長 100um 的一段,此過程使用了 AWR APLAC HB 模擬與 AWR AXIEM 3D Planar EM 分析。

圖 10:Layout 中的漏極多支路結構過渡 (左) 和 EXTRACT 模擬前後的比較 (右) 。

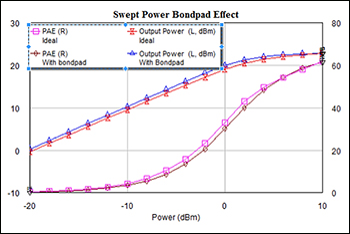

後續的 PAE 和 Pout 模擬也表明,這些相對較小但有必要的特徵會引起非線性性能下降。相比之下,鍵合焊盤本身 (圖 11) 的變化非常小。

圖 11:理想的功率放大器與在功率放大器輸出端增加三個平行鍵合焊盤後的非線性性能對比。

第 6 步:最終分析

在最後的分析步驟中,我們要在整個設計的背景下 (既然設計似乎已經完成) 重新審視創建設計時採取的設計假設和簡化措施。透過該步驟,設計師能夠確保整體至少是各部分的總和,並且在關注設計各個部分的過程中 (即將設計分割成較小的部分) ,其中的任意兩個部分沒有在無意中被耦合在一起,從而使整體性能受到影響。從這個角度來看,可以將這一步看作是上升一個層次,設計參數是子塊 (輸入匹配、輸出匹配、FET / 負載、偏置電路等) ,而不是子塊中的各個元件。性能標準是整體的晶片要求,一旦相對於分析物件的性能標準得到滿足,就實現了設計收斂,分析物件包括:電磁的電氣性能、熱可靠性、DRC 可製造性等等。

分析是為了確保二階效應 (如電磁耦合和熱效應) 不違反早期的設計參數約束和假設。電磁分析將驗證關於源極電感和互連寄生的假設,這可能會影響回饋路徑,從而增加不穩定性。電磁分析十分耗時,需要使用記憶體配置較高的工作站,但電磁分析越詳細,就越有可能發現潛在振盪或導致性能欠佳的寄生效應。現在,AWR AXIEM 分析和 EXTRACT 流程等電磁模擬應該在頂級晶片上運行,而不只是單獨考慮每個設計子塊。在這兩者之間反復運行是一個很好的策略,可以隔離此時發現的任何問題。

正式的有限元素法 (FEM) 熱分析再次確認了通道的工作溫度。經過十餘年的發展,電磁分析已經足夠穩健,可以納入 MMIC 設計師的流程中,熱分析也是如此。儘管熱分析剛出現不久,而且與電氣工程師可能熟悉的其他步驟不同,但在 MMIC 工具集中,熱分析非常簡單,也非常有用,不進行熱分析就太可惜了。為功率放大器設計的許多假設提供支援的是 FET 通道的工作溫度。在佈線確定後,所有的金屬化流程都已完成,透過電熱分析,我們可以再次確認關於 FET 通道間距和直流偏置的決定是否妥當。整合在 AWR 軟體中的 Cadence Celsius Thermal Solver 可以在幾個小時內完成這一流程。

如果電磁或熱驗證步驟因沒有實現設計收斂而失敗,可以增加互連的寬度或縮短互連的長度,以儘量減少電感,或增加互連間距以避免電容,也可以增加 pHEMT 導引之間的間距,以加強通道散熱。簡而言之,對於 GaA pHEMT 功率放大器設計師來說,在許多情況下可以把熱考慮作為一種次要影響,在驗證期間通過一個分析步驟來處理。當然,並不是要處理激進的熱規格或可靠性要求。

這一步的問題是,設計師實際上可能成功地發現設計中的問題。因為設計參數已經被抽象化了,如果分析沒有與設計要求形成收斂,那麼設計師就有可能不知道要修正什麼 (即移動哪個互連,縮短哪個鍵合線等等) 。分析工具會指出設計存在問題,但如果沒有能力透過參數化模型直接將因果關係聯繫起來,最好是憑藉經驗判斷。無休止地花幾天或幾周的時間反復“移動一條線,運行一次電磁模擬”很少能找到答案。最後且同樣重要的是,需要實現設計到製造的收斂:在交付設計時,一定要附帶基於代工廠的設計規則檢查 (DRC)。AWR Microwave Office 軟體包括 DRC 和電路佈局驗證 (LVS) 工具,而一些代工廠在一天或更短的時間內就可以為設計師完成這一工作。

結論

從一種技術切換到另一種技術,要求某些技能和知識是可以轉移的。這些技能中最基本的是有效使用電子設計自動化 (EDA) 工具來設計 MMIC。特別是,功率放大器設計師需要一種戰略、設計流程和指導方針,以瞭解如何從規格和 PDK 開始,直到可以應對更複雜的設計要求。

本文使用 AWR Microwave Office 軟體設計了一個相對基本的 A 類 GaA pHEMT MMIC 功率放大器,並以此為例說明了典型的功率放大器設計專案的必要步驟。選擇 A 類放大器是為了強調流程本身,以及設計師需要採用系統的方法來處理自己的設計和設計流程。事實表明,在設計流程中的每一步,必須清楚地確定所設計的內容,將參數與性能聯繫起來,並且設計師要知道怎樣才算完成了相應的步驟。這種設計方法可以輕鬆擴展,應用於更複雜的功率放大器和其他電路類型。

參考文獻

1. | M. Steer, Microwave and RF Design: A System Approach, SciTech Publishing, 2010. |

|---|---|

2. | S.A.Maas, The RF and Microwave Circuit Design Cookbook, Artech House, 1998. |

3. | D. Wu and S. Boumaiza, “Comprehensive First-Pass Design Methodology for High Efficiency Mode Power Amplifer, ” IEEE Microwave Magazine, Vol 11. Issue 1, pp 116-121. February 2010. |

4. | G. Gielen and R. Rutenbar, “Computer-Aided Design of Analog and Mixed-Signal Integrated Circuits, ” Proceedings of the IEEE, vol. 88, no. 12, pp. 1825–1854, Dec. 2000. |

5. | S. Nuttinck, B.K. Wagner, B. Banerjee, S Venkataraman, Ed. Gebara, J. Laskar, H.M. Harrais, “Thermal Analysis of AlGaN-GaN Power HFETs, ” IEEE Transactions on Microwave Theory and Techniques Vol. 51, No. 12, pp 2445-2452, 2003. |

6. | M. Alvaro, A. Caddemi, G. Crupi, N. Donato, “Temperature and bias investigation of self heating effect and threshold voltage shift in pHMET’s, ” Microelectronics Journal, Vol. 36, pp. 732-736, 2005. |

7. | S. C. Cripps, RF Power Amplifiers for Wireless Communications, 2nd edition, Artech House, 2006. |

A. Platzker and W. Struble, “Rigorous determination of the stability of linear n-node circuits from network determinants and the appropriate role of the stability factor K of their reduced two-ports, ” Third International Workshop on Integrated Nonlinear Microwave and Millimeterwave Circuits, pp. 93-107, 1994.

致謝

特別感謝在射頻 / 微波領域聞名遐邇的 Michael Heimlich 博士,他於 2001 年加入 AWR,如今是澳大利亞麥考瑞大學的教授。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」