本文要点

阻抗决定信号的传播行为,互连器件上的每个功能元件都有一定的阻抗。 |

|

对于差分信号,过孔会有自己的差分阻抗,就像差分对中的走线具有特定的阻抗一样。 |

|

影响差分对过孔阻抗的因素,会影响在过孔处观察到的输入阻抗。 |

高速 PCB 和信号标准对差分对的使用几乎都有如下要求:精确的阻抗、长度匹配、信号偏移补偿和损耗预算。为了达到此类重要的差分信号完整性目标,设计人员需要借助工具,精确地计算阻抗,以及了解差分信号与互连器件上各个功能元件的交互方式,如连接器、电缆、元件和过孔。

过孔应以差分方式排列,就像走线对一样。过孔对有自己的差分阻抗,因此也有自己的网络参数集 (即 S 参数)。那么,有哪些因素会影响差分对的过孔阻抗?

这些差分对上的过孔有自己的阻抗,这可能会在长互连中造成信号完整性问题

了解差分对过孔阻抗

正如 PCB 上的走线一样,过孔也有自己的阻抗,通常使用集总电路模型来描述,类似于传输线。了解过孔如何像一个简单的电感器、LC 电路或纯电容器一样工作,将有助于了解过孔的结构和附近的寄生效应对过孔的差分阻抗有何影响。

以下因素将共同决定单个过孔的特性阻抗:

过孔电感 | |

每个过孔都像一个充满弱磁芯的小型电感器。虽然它们不会像大型电磁铁那样产生很强的磁场,但它们仍然具有电感阻抗。 | |

与附近平面的寄生电容 | |

波传播的方向要求波与不同类型的不同阻抗相互作用。一个阻抗下的相互作用会影响后一个阻抗下的相互作用。 | |

PCB 层压板材料 | |

PCB 层压板的介电常数也会影响单个过孔的阻抗。 |

一旦使用差分信号驱动两个过孔,它们的差分阻抗将由其寄生电容和电感耦合决定,就像偶模和奇模传输线一样。确定差分阻抗后,我们现在需要计算出 (差分对) + (通孔) 组合的输入阻抗,这决定互连中的 S 参数。

差分过孔的输入阻抗

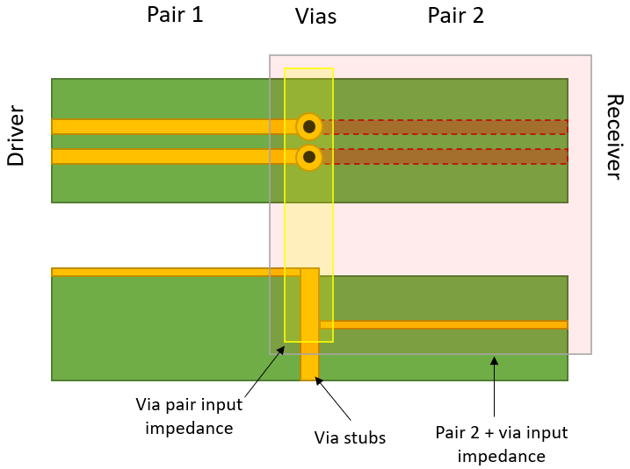

对于带有差分过孔结构的互连,其差分阻抗的计算是一个迭代的过程;从接收端开始计算输入阻抗,然后回到负载端。下图解释了具体的原理。图中有一对位于驱动器和接收器之间的差分对,中间有一对差分过孔。

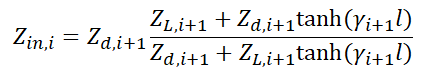

互连的每个部分都有自己的输入阻抗。每个部分的差分输入阻抗取决于所有下游部分的差分阻抗,这有点类似于标准传输线。我们可以写出以下迭代方程,有关互连线 i 段的输入阻抗和下一段的输入阻抗:

输入阻抗方程

该输入阻抗将决定传输线各段的反射。对于通过过孔对的差分信号,过孔焊盘处的输入阻抗可能与差分对 2 的差分阻抗相似,具体取决于过孔的长度和传播延迟。

与传输线一样,差分过孔也有一个临界长度,决定了是否需要与两侧的差分对进行精确的阻抗匹配。如果过孔长度较短,那么 tanh 函数将近似为 0,输入阻抗将是 (i + 1) 段的差分阻抗。低速/低频信号就会出现这种情况,因此我们通常不用担心 10/100 以太网、低速 USB 或类似差分协议的差分阻抗。但对于其他协议,如千兆以太网或 MIPI 协议,过孔长度非常重要,应该采取措施了解差分对过孔阻抗对互连损耗的影响。

差分过孔的挑战

经过上文的讨论,我们总结了以下几点:

差分过孔对非常短时,其阻抗并不重要;此时过孔对的输入阻抗等于差分对 2 的输入差分阻抗。 |

|

过孔对非常长时,例如在较厚的背板中,差分过孔对的阻抗将决定传播信号的阻抗失配。 |

|

过孔 stub 是阻抗失配的另一个来源,当 stub 较长时,会产生差分谐振。 |

使用短过孔和较短的 stub

要确定具体的应用场景,需要查看过孔的临界电气长度。一般来说,对于带宽高达 100 GHz 左右的信号,要使用较短的差分过孔对和背钻技术以留下较短的过孔 stub。这样解决了两个问题,但却增加了布线和堆叠设计的复杂性,并增加了系统的总成本。

使用差模 S 参数

要全面总结过孔对的行为,我们需要借助差模 S 参数。差分对的过孔阻抗与这一部分的输入阻抗不匹配时,就会产生一定程度的回波损耗。高速通道中的总损耗 (回波损耗加插入损耗) 需要与差分通道中的损耗预算进行比较,而损耗预算将在接收器规格中指定。

一流的 PCB 设计软件会包含3D 场求解器,可以直接根据 PCB layout 计算 S 参数和其他网络参数。Cadence Clarity 3D Solver 可以帮助用户快速取得精确可用的 S 参数模型以进行系统分析,并强调精准度、无限容量与速度三者并行,欢迎点击了解更多 Cadence Clarity 3D Solver 。

译文授权转载出处 (Graser 协同校阅)

长按识别 QRcode,关注「Cadence 楷登 PCB 及封装资源中心」