By Paul McLellan, Cadence

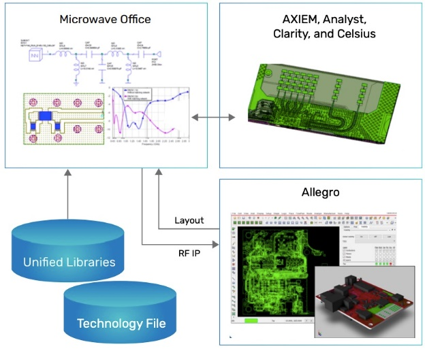

去年 AWR Design Environment® 推出的新版本 V16 具有跨平臺的工作流程,支援基於 Virtuoso® (晶片) 和 Allegro® (PCB / 封裝) 平臺的射頻到毫米波設計,並與系統級分析解決方案 Clarity™ 3D Solver 和 Celsius™ Thermal Solver 整合。新版 AWR Design Environment,包括 Microwave Office® 電路設計軟體,使客戶能夠為汽車、雷達系統、5G 等應用設計互聯系統。與同類競品的工作流程相比,AWR 緊密整合的平臺可以將周轉時間加速高達 50%,其射頻整合水準在業內也是首屈一指。

射頻設計一直是電子系統設計中最複雜的領域之一。所有元件,甚至是不相關的金屬片,都會互相影響。其中的一項挑戰一直是缺乏良好的整合設計工具。20 年前諾基亞副總裁曾表示射頻設計師非常稀少,他用一個 excel 表格就列出了所有全球有能力的射頻設計師以及他們的工作地點和聯繫方式。與現在相比,20 年前的射頻設計更像是一門黑科技,因為除了模擬之外,基本上沒有任何射頻設計和分析工具。但是在那時,Cadence® Spectre® RF 就已經問世了;同時,Virtuoso 工具可以用來在多邊形層面上佈置任何電路,包括射頻電路。但僅此而已。射頻設計依然是需要大費周折手工製作的模擬設計。

如今的情況已經有了很大的改善,無論是在有能力進行射頻設計的設計師數量方面,還是在可用設計工具的範圍和品質方面。與手機剛問世時相比,射頻設計已經成為家常便飯——彼時想讓收音機正常工作都是一個挑戰。

今天,隨著 AWR V16 版本發佈,高效的設計工具組合又向前邁進了一步。5G 是大家關注的熱點,但事實上,還有很多其他基於無線電的通信系統也很重要,從 WiFi 6 到藍牙,再到 Zigbee 等等。事實上,在資料中心之外,有線連接越來越少 (而在資料中心內,使用越來越多的是光學連接)。筆記型電腦可能是通過 WiFi 連接到網路,通過藍牙連接到鍵盤和滑鼠,以及 Zoom 耳機和話筒。不久以前,所有這些都是有線連接。手機設備具備以上所有功能,更具備高速資料網路連接 (5G、LTE、4G 語音、4G 資料,以及更早的標準) 和 GPS;當然 GPS 只是用於接收信號,並不能向衛星發射信號。

從無線電的角度來看,5G 是兩個完全不同的標準,即 6GHz 以下 (也稱為低頻和中頻) 和毫米波;後者不是指剛剛超過 6GHz 的頻段,而是在無線電頻譜上的 24-100GHz。5G 實際上有無限的頻寬可用,但也面臨嚴重的挑戰:5G 信號不能穿過牆壁或車窗,而且只能在空中傳播幾百米。這個頻率與 6GHz 以下的頻段有很大的不同,它需要不同的無線電和不同的波束賦形方法。如果想要更進一步瞭解毫米波這項技術,請閱讀文章《產業觀察 | 如何從技術角度看待 5G 毫米波的商用價值》。如果以上內容聽起來足夠有挑戰性,那麼 6G 則更勝一籌,進入了所謂的太赫茲 (Terahertz) 頻段,實際上大約是 500+GHz。

AWR V16 版本有很多新功能,最重要的幾項包括:

與 Allegro 整合:確保與 PCB 和 IC 封裝設計流程的製造相容性和射頻整合 |

|

與 Virtuoso 整合:利用 AWR Microwave Office 完成射頻前端設計 IP,並將其與 Virtuoso Layout Suite 結合使用,以進行積體電路和模組整合 |

|

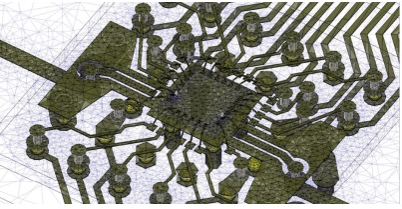

與 Clarity 3D Solver 整合:支援 EM 分析,用於大型射頻結構的設計驗證,例如模組封裝和相控陣饋電網路 |

|

與 Celsius Thermal Solver 整合:為單片微波 IC (MMIC) 和 PCB 高功率射頻應用提供熱分析 |

|

AWR 增強功能:利用設計自動化和有限元分析 (FEA) 求解器性能的增強,加速射頻 IP 的創建 |

這些整合並不都是獨立的,而且可能都需要一起運行;因為一個基於射頻的現代系統可能包括天線、PCB、封裝、帶有無源器件和發射機的中介層,以及帶有無源器件和大部分射頻電路的晶片。AWR V16 技術簡介中有這樣一段話:

「先進的整合方法帶來了尺寸更小、更高效的系統。然而,這些高度整合的系統也更複雜,更容易出錯,因為各個元件相互依賴,具有跨結構互連的複雜網路,以及從多個來源彙集跨平臺組裝設計數據的挑戰。為了解決這些設計障礙,AWR Design Environment V16 為開發 MMIC 和射頻 PCB IP 提供了一個增強的平臺。設計團隊可以透過 Cadence EDA 軟體組合中的成熟功能,包括用於 PCB 和系統級封裝 (SiP) 設計的 Allegro 平臺,以及用於 RFIC和模組的 Virtuoso 平臺,將他們的 MMIC 和射頻 PCB IP 納入由 IC 和中介層、PCB 以及模組組成的電子系統中。」

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」