By Cadence

5G 無線系統和連接設備正在每一個可以想像的行業中激增,促使技術領先者利用市場機會,開發由性能、尺寸和成本決定和區分的射頻產品。傳統上,利用最新先進技術節點的定制或專有積體電路 (IC) 設計一直是實現差異化的途徑,但今天的複雜設計正在超越只考慮晶片內部設計的界限。

射頻和混合信號設計工作不僅包括多樣化的半導體工藝,還包括先進的跨層封裝和系統級封裝 (SiP) 和封裝中的封裝 (PiP) 技術,以及使用先進互連技術實現的 3D-IC。成功的產品需要在開發的整個設計、分析和簽收階段,在系統層面上考慮可能影響最終產品整體性能的每一個可能的元件之間的相互影響。所有影響結果的電氣因素——微觀和宏觀的——都必須考慮。

為了在競爭激烈的 5G 無線市場中獲勝,公司需要電子設計自動化 (EDA) 解決方案實現從晶片到系統的完整和全面的射頻工作流程。為了實現這一目標,工程團隊需要融合 EDA 平臺以及模擬和分析技術,以確保寶貴的工程時間用於設計,而不是將資料從一個工具轉移和翻譯到另一個工具。EDA 軟體發展商必須提供一個高效的前端到後端的交互操作工作流程,以最大限度地提高用戶的生產力。

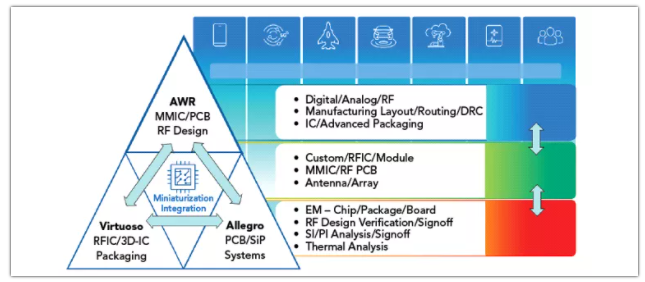

隨著 Cadence 在 2020 年從美國國家儀器公司收購了 AWR®,Cadence® AWR Design Environment® 平臺的最新 V16 版本提供了完整和全面的RF工作流程 (圖 1)。

圖 1:Cadence 射頻 EDA 解決方案提供了一個全面的設計工作流程。

異構技術

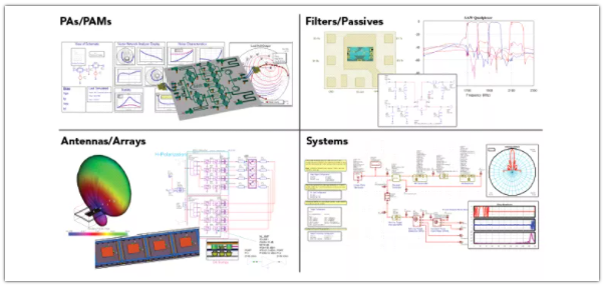

異構整合減輕了同構系統晶片 (SoC) 解決方案的高成本壓力,使設計者能夠在使用較新的封裝技術的基片上結合成熟的 RFIC 和 MMIC 設計。先進的整合方法,如扇出式晶圓級封裝 (fan-out wafer-level packaging) ,可以產生更小、更有效的系統,然而這些高度整合的系統更加複雜,容易因各個元件的相互依賴性、複雜的跨結構互連網路以及從多個來源彙集跨平臺設計資料的挑戰而產生錯誤。平臺的互通性對於跨晶片、封裝和電路板設計的多技術整合至關重要 (圖 2)。

圖 2:AWR 軟體平臺支援從 IC 到系統的設計。

新發佈的 AWR Design Environment V16 版本透過工作流程自動化使周轉時間減少至少 50%。它透過利用射頻智慧財產權 (IP) 創建和跨平臺模擬,包括 IC 和封裝 (Virtuoso工具流程) 和電路板 (Allegro工具流程) 來實現這一目標。此外,Clarity™ 3D Solver 和 Celsius® Thermal Solver 的整合和互通性提供了電熱協同模擬和如射頻前端這樣的大規模高密設計的耦合分析。V16 版本實現的射頻工作流程創新始於在不同的加工領域對應的設計平臺間設計資料和軟體 IP 的共用和傳輸方式的基礎性進步。在 Cadence 旗下,V16 軟體所引入的射頻整合水準顯著提高了工程團隊的生產力。

Cadence 的工具平臺不斷發展,以解決所支援的工藝技術的製造、設計和分析要求。其設計流程自動化可管理極其複雜的晶片、封裝和電路板系統的開發。由於系統級整合要求跨這些不同的技術進行射頻設計,在開始設計之前,工程師要從多個來源獲取資訊:業務需求、可靠性約束、製造工藝和供應鏈資料。對於企業和大型設計團隊來說,需要有效地共用庫,使用公司授權和預先批准的元件和疊層材料進行工作,這增加了將產品快速推向市場的挑戰。為了共用設計資料、利用不同工具的獨特功能、減少或消除系統整合瓶頸,平臺之間的互通性是必要的。射頻設計和加工版圖設計團隊之間的任何脫節都會消耗工程資源並直接影響開發進度。

想像一下,在 AWR 軟體中創建的射頻 IP 可以無縫地整合到用較新的工藝技術和整合方法設計的系統中。開發團隊現在有一個高效的射頻工作流程,使他們能夠提取 AWR 射頻 IP/設計資料,並在適當的 RFIC、PCB 或 SiP 平臺上重複使用。AWR V16 版本引入對 Cadence 統一庫和技術檔的支持,建立了 AWR、Virtuoso 和 Allegro 平臺之間的互通性。

Virtuoso 和 AWR 工作流程

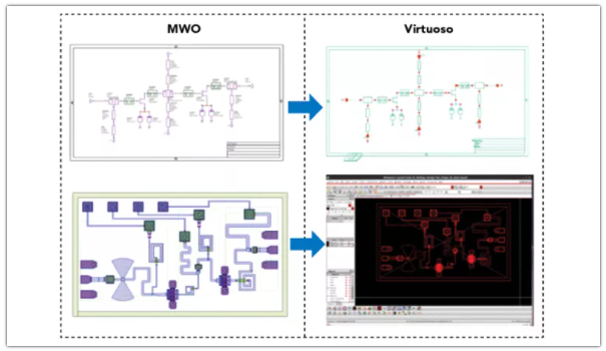

利用 Cadence EDA 解決方案的共用架構和資料,AWR V16 版本提供了新的射頻工作流程,從 Microwave Office 軟體中獲取完整的設計,並將電路圖和版圖設計傳遞給 Virtuoso 和/或 Allegro 平臺。這些資料在一個統一的庫中,包含了電路設計的所有構建塊。這使設計團隊能夠操作 Allegro SiP 或 Virtuoso SiP 雙向實現流程和 Virtuoso RF Solution 物理實現流程作為主要版圖設計工具,其射頻 IP 電路圖和版圖設計資料由 V16 軟體提供。Virtuoso RF Solution 流程可捕獲 Microwave Office RF IP,使設計人員能夠在單一環境中展示、整合和驗證 MMIC 和嵌入式 RF 封裝設計。共用資料庫通過簡化設計流程,輕鬆可靠地訪問 Microwave Office 內開發的 RF IP,實現了更實用的封裝和 IC 協同設計。

例如,Microwave Office 使用者可以透過電路設計、優化和電磁驗證來設計片外無源元件,然後決定最佳的實現技術。在某些情況下,最好的無源元件網路可能需要跨越 IC 和封裝的邊界來實現。對於射頻模組來說通常是這樣,理想的濾波器設計、匹配網路和功率放大器輸出級的負載終端同時使用了晶片和封裝基板上的元件。

在 Virtuoso 射頻解決方案環境中,Spectre® 模擬平臺引擎可以模擬 Microwave Office 線性模型,支援帶有嵌入式 Microwave Office IP 的 IC 和模組協同設計。將該 IP 導入 Virtuoso 流程的能力延伸至 MMIC 設計。由於大多數 MMIC 模型和 PCell 庫是由 III-V 代工廠作為工藝設計套件 (PDK) 定義和實現的,Microwave Office MMIC 設計流程會在設計中使用該 PDK 的目標半導體工藝。由此產生的 MMIC 電路圖和佈局可以作為一個統一的庫設計匯出,並導入 Virtuoso 環境 (圖 3)。

圖 3:從 AWR 導入 Virtuoso 的兩級 MMIC 放大器設計。

ALLEGRO 和 AWR 工作流程

從 IC 到電路板,一個 RF 設計的 PCB 工作流程開始於從 Allegro 部件和電路板定義創建統一的庫和技術檔 (technical files) 。AWR V16 軟體中新的統一庫導入嚮導讀取通用庫和技術檔中的 Allegro 符號 (symbols) 和接腳圖 (footprints) ,並將這些資料轉換為 AWR PDK,可用於使用標準設計輸入和模擬方法創建射頻設計。完成設計後,射頻工程師使用 AWR V16 軟體中的一個新工具,將子電路的電路圖和版圖設計包括所有底層層次匯出到統一庫設計中 (圖 4)。

圖 4:使用 V16 導入嚮導的 Allegro RF 至 PCB 工作流程。

在後端,版圖設計工程師需要訪問根據公司批准的材料清單 (BOM) 和目標製造工藝設計的完整資料。基於 Allegro 源自組織批准的 BOM 和工藝技術的部件,射頻工程和佈局團隊能提高設計移交的效率和可靠性,同時減少射頻設計和製造要求之間的差異導致的來回協調。

多物理場

歷史上,大型射頻結構,如相控陣饋電網路,一直被手動分割成較小的結構,使用最大和性能最強的計算資源進行分析。AWR V16 版本整合了用於設計關鍵互連、RFIC、MMIC、模組、PCB 和 SoC 設計的 Clarity 3D Solver 3D 電磁模擬器,通過利用 Cadence 的分散式並行處理技術,克服了傳統電磁分析軟體的限制,該技術以 10 倍的速度提供了幾乎無限的容量。Clarity 3D 求解器為射頻設計者提供了隨時獲得高容量電磁分析的機會,用於大型複雜射頻/混合信號系統的設計驗證和簽核,得到了超越 AWR AXIEM 3D 平面和 AWR Analyst 3D 有限元方法 (FEM) 求解器所提供的處理能力。

Clarity 與 Microwave Office 平臺的整合是一個自動化過程,整個模擬設置操作完全在 AWR 環境中進行。一旦模擬完成,一個包含輸入幾何結構、模擬設置和 S 參數結果的資料集就會自動組裝起來,並與給定的電磁檔相關聯,用於繪圖、測量和隨後的提取、電路模擬、調整和優化。該連結除了支援 S 參數外,還支持網格剖分結果、電流分佈和電磁場分佈視覺化資料,使設計人員能夠使用 AWR Design Environment 平臺中已有的豐富的三維電磁結果顯示 (圖 5)。

圖 5:Microwave Office V16 使用 Clarity 提供大規模的電磁分析。

熱分析

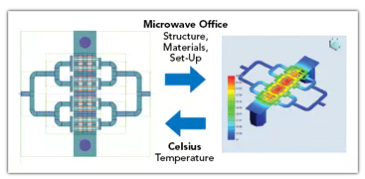

晶片電路和電子系統公司,特別是那些使用積體電路封裝和/或多技術模組的公司,面臨著可能破壞專案進度的晶片散熱挑戰。AWR 軟體中的 Cadence Celsius 熱解器為射頻器件、PCB 和模組設計提供了一個解決方案,支援使用來自 AWR Microwave Office 軟體的模型資訊進行電熱分析,使用現有的 MMIC 設計資料和幾何形狀,如版圖設計、材料屬性和來自射頻模擬的功耗值。解算器在 IC 版圖的相關解析度下提供完整的 IC 溫度分佈結果,可作為圖形化的 3D 溫度疊加,以及返標溫度回網表用於電路模擬 (圖 6)。

圖 6:用 Celsius Thermal Solver 進行耦合電熱分析。

熱分析提供了關於工作溫度可能降低射頻性能和威脅器件可靠性的洞察力。通過在 Celsius Thermal Solver 中直接使用從 Microwave Office 軟體中獲得的模型和功耗資訊,設計人員可以實現更準確的分析結果。額外的物件如散熱器等也可以添加進來,和晶片一起作為一個新的結構匯出,用於熱分析,這使設計者能夠研究散熱器策略,得到最好的散熱方案。

隨著射頻系統的激增和採用異構技術整合以在更小的空間內實現更大的功能,設計平臺和多技術工作流程必須具有互通性。AWR Design Environment V16 平臺包含了創新的功能,通過在 Virtuoso 和 Allegro 設計平臺內對 AWR 平臺射頻/微波設計 IP 的無縫跨平臺和多物理學整合,以及透過 Clarity 和 Celsius 求解器對完整的大規模設計進行電磁和熱分析,提高工程生產力。

從晶片到系統,工程師可以在 Cadence 提供的全面的從前到後的射頻工作流程中更好地解決跨結構、多技術的產品開發挑戰。AWR V16 正在進一步簡化產品開發、提高使用者生產力,消除設計人員在孤島式工具之間切換的非生產性時間和交互週期所帶來的低效率和洞察力損失。

本文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」