何時應使用阻抗匹配網路,哪種網路適合系統?

答案是:「視情況而定」。如果設計兩個零件之間的互連線時,源和負載的阻抗不匹配,那麼則很有可能需要一個匹配網路。

是否需要阻抗匹配網路?

答案取決於信號的上升時間和沿互連線的傳播延遲。如果傳播延遲超過信號上升時間約 50%(對於數位信號),或者超過振盪週期的四分之一(對於類比信號),則需要考慮阻抗匹配。

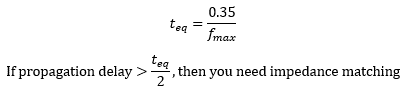

對於需要輸出一系列類比信號的放大器,在確定阻抗匹配需求時,需要考慮所需的最大輸出頻率。這通常透過取最大輸出頻率(fmax),並轉換為振盪週期,再將其轉換為等效上升時間(teq)來實現。對於最大輸出頻率,該等效上升時間等於振盪週期的 35%。一旦傳播延遲超過該上升時間的 50%,就需要阻抗匹配。

圖 1:放大器阻抗匹配的條件

阻抗匹配網路

首先,需要注意的是,通常只需要為負載或源元件,而不是同時為兩者設計阻抗匹配網路。這是因為傳輸線的阻抗可以透過調整其幾何形狀來調整。如此一來,可以立即將走線阻抗與源或負載匹配,同時一個匹配網路將連接到另一個零件。

通常,每條單端傳輸線與源的阻抗都匹配,而且有一個匹配網路與負載連接。目標是改變由負載 + 匹配網路形成的等效電路的阻抗,使其匹配傳輸線的阻抗。

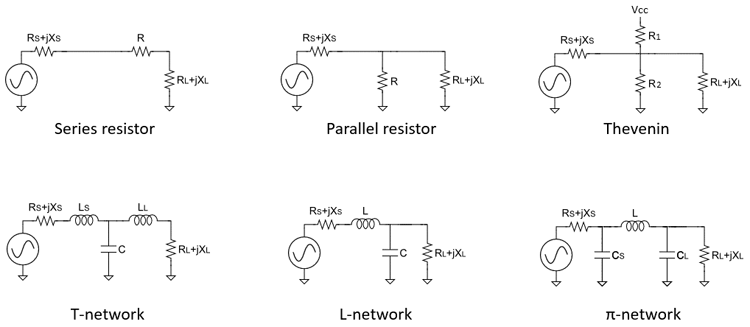

可供選擇的有幾種阻抗匹配網路:最簡單的匹配網路將電阻與負載串聯或並聯(接地)。例如,如果源和傳輸線具有相同的阻抗,但負載的輸入阻抗非常小,則可以將一個電阻連接到負載的輸入埠,使其阻抗增加,以匹配傳輸線的阻抗。

電阻並聯的話,會得到相反的效果。並聯電阻有效地降低了負載 + 端接電阻並聯電路的等效阻抗,使其與傳輸線的阻抗相匹配。下圖展示了六種有效的阻抗匹配網路:

圖 2:源阻抗和負載阻抗的一些常見阻抗匹配網路

請注意! 以上所示的源和負載的電路模型包括輸出和輸入電抗值,這些值通常僅由電容決定。輸出 / 輸入電容通常可以在相關部件的資料手冊中找到。元件模型中的輸出 / 輸入電容需要與輸出/輸入電阻並聯,電阻值的選擇需要與目標頻率下的準確阻抗值相匹配。

設計和類比阻抗匹配網路

通常在特定頻率或特定波形下類比阻抗匹配網路。涉及類比信號時,一些工程師發現在頻域中設計更為容易。但是,如果不熟悉頻域SPICE模擬,也可以使用正弦電壓源在時域中進行。涉及數位信號或任意波形時,在時域中設計和模擬會好很多,因為頻域類比需要估計這些信號的功率頻譜。

首先將一個源與一個具有規定阻抗的等效電阻串聯,進行模擬;然後,將其串聯到一個具有規定阻抗的電阻上,從而模擬傳輸線;最後,將其串聯到負載,負載用一個具有規定阻抗的電阻表示。

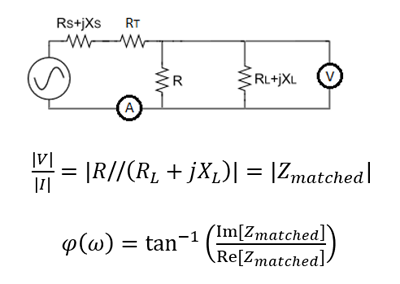

為了確定網路是否與傳輸線的負載阻抗匹配,需要測量流經網路的電流和網路上的電壓降。透過計算電壓電流比可以得到阻抗;還可以計算匹配網路中累積的相位差。

圖 3:並聯電阻阻抗匹配網路中電壓和電流的大小和相位差的方程式

一旦建立了確定負載阻抗的模型,就可以調整阻抗匹配網路中電路元件值,從而確定匹配的負載何時具有所需的阻抗值。這需要迴圈訪問連續的電路元件值。然後,可以使用 Optimizer(優化器)來確定匹配阻抗所需的確切元件值。

關於阻抗受控佈線的說明

阻抗受控佈線是一種很好的方法,可確保走線的阻抗值與電路板中各種源和負載的阻抗匹配,進而確保電路板中大多數互連線的阻抗匹配。許多根據特定信號標準專門設計的元件可實現特定的阻抗值,因此只需考慮設計出與特定阻抗匹配的走線幾何形狀。

然而,即使使用特定的信號標準,也並非所有元件都能實現阻抗匹配,而且受控佈線也不能消除特定互連線中的阻抗不匹配。因此,應始終分別檢查負載 / 源的輸入 / 輸出阻抗,確定哪些互連線需要阻抗匹配網路。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」