本文要點

為什麼在 PCB 設計中需要使用功能性分區 |

|

設置功能性分區時的注意事項 |

|

利用 PCB 設計工具的功能和特性來創建分區 |

在 PCB 的設計中,往往採用了分區原理,即有不同的電路組來完成不同的功能,從而防止不同組電路之間產生干擾,使電路板正常運行。讓我們來仔細瞭解一下 PCB 設計中的功能性分區,以及 CAD 工具如何幫助我們實現這一目標。

( 中文字幕 / 英文配音 )

溫馨提醒 : 可點擊影片下方設定圖示, 在 Captions 中選擇國語, 開啟中文字幕觀看

PCB 設計中功能分區的用途

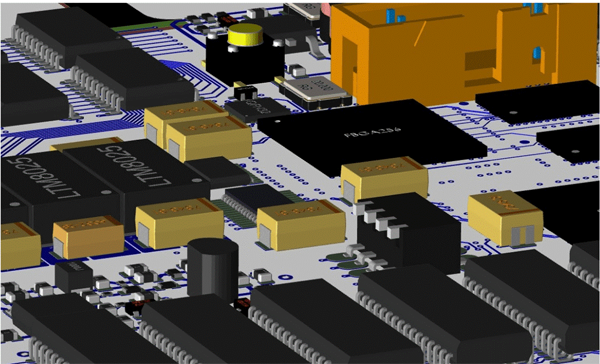

一塊電路板是由不同類型的電路組成的,所有的電路都聚集在一個相對較小的區域內。我們通常會發現,同一塊電路板會同時使用類比、數位和電源電路。即使是以數位操作為主的電路板,通常也會有一些需要管理的電源,以及需要將類比信號轉換為數位信號,然後再轉換回來的介面。

在電路板上指定功能性分區的目的就是讓這些不同的區域相互隔離。以下是混合信號電路板中存在的一些問題,而分區將有助於避免這些問題:

串擾: |

|

攻擊性 (aggressive) 信號可能會與其他信號耦合在一起,應該盡可能將其與潛在的受害者 (victim) 信號隔離開來。 |

|

電磁干擾 (EMI): |

|

為了防止電磁干擾,需要防止不同區域的返回信號混合在一起,並且需要阻止它們穿過分裂的地面或電源平面。 |

|

信號完整性差: |

|

時脈等敏感信號需要緊貼相關電路,而不是在整個電路板上游走。 |

|

電源雜訊: |

|

這些組件應該靠近它們供電的元件,並在同一層上運行,為它們提供一個隔離的相鄰參考平面。 |

隔離這些區域有助於防止一種類型的電路產生的雜訊影響另一種類型的電路。但問題是,不能簡單地在電路板的中間畫一條線來分離數位和類比電路。這些電路組需要彼此互動,而且還必須接入電路板不同位置的連接器和其他介面器件。

因此,要想設計出能正確隔離這些區域的 layout,就需要制定良好的功能分區計畫並妥當放置組件。

功能分區還有其他一些好處。透過提前對分區進行佈局規劃,layout 設計團隊在進行元件放置時將會更有條理。此外,設置分區還有助於 layout 團隊在放置用於 DFM、測試和返工的組件時做出更好的選擇。

平衡功能分區的需求和其他元件的放置需求,聽起來好像一下子要完成很多工,但對於 PCB layout 專家來說,這些都是工作的一部分。那麼,讓我們深入瞭解一下如何在 PCB 設計中有效劃分功能分區。

在 layout 設計開始之前,制定完善的功能分區計畫將為 PCB 設計帶來很多益處。

在規劃分區的同時規劃零件的放置位置

與任何 PCB 設計一樣,在開始放置零件之前,必須先確定實體電路板的配置。首先,必須確定電路板的尺寸和形狀,以及任何固定零件的位置,如連接器、支架或開關。這對於電路板的分區來說是必不可少的,因為在 layout 設計過程中,電路板輪廓發生改變會導致零件偏離規劃的分區。

同時,必須確定電路板層的堆疊。對於高速設計,很多佈線必須包含在特定的層對之間,這些層對是為帶狀線佈線而設置的。要規劃出分區,就必須根據層堆疊配置來評估佈線密度。

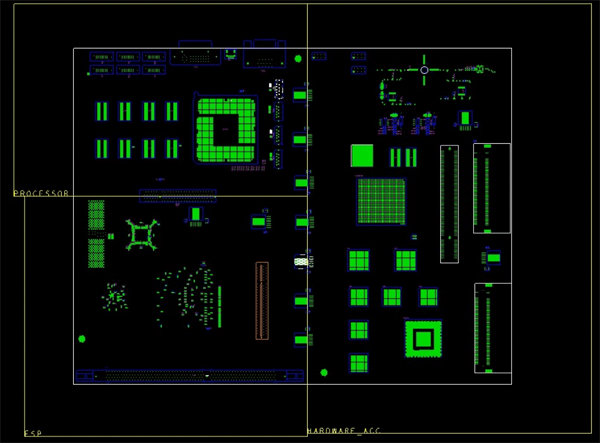

在確定了電路板的物理配置後,我們就可以開始繪製設計的功能分區。這期間所做的許多決定與放置零件時的決定類似,所以我們來回顧一下必須滿足的要求:

使放置零件的類比和數位區域彼此分離

分離這兩種電路是分區設計的主要目的,然而,在零件放置過程中,它們往往會被混在一起。在過渡到 layout 之前,在電路圖上根據零件的功能進行分組將對繪製分區很有幫助。

將電源與敏感元件隔離

雖然電源需要足夠接近相應的零件,以便為後者供電,但電源電路和它們為之供電的數位零件之間必須相距一定的空間。

規劃集中在電路板上的大型 CPU 和記憶體元件

這些零件不應該靠近邊緣,以便透過電路板散熱。但與此同時,為了保證信號的完整性,它們的放置位置應該足夠靠近相關電路。

相關電路應歸入同一分區中

利用電路圖中的邏輯流程來繪製分區。從連接器著手,根據電路圖中的電路佈局方式,從連接器開始放置零件。

我們所創建的大部分分區都將基於零件和零件之間的網狀連接。然而,在繪製分區時,需要考慮一些佈線問題,我們接下來將具體分析。

簡單的 PCB 設計功能性分區示例。

走線佈線和功能分區的其他考慮因素

當我們為設計規劃分區時,請記住,除了它們將包含的零件外,分區還必須考慮到佈線問題。大型資料和記憶體匯流排將佔用大量的空間,尤其是在外部層上對其進行佈線時。一些零件需要空間來進行竄走佈線,這樣就不必為了縮小分區而把所有的零件擠在一起。我們還需要為不能通過某些電路區域進行佈線的敏感網路留出空間,例如通過類比電路區域運行數位網路。

繪製電路板分區最重要的一個方面是設計電源分配網路 (PDN)。以下是一些需要牢記的重要 PDN 準則:

儘量避免分割平面。如果必須分割一個平面,請一定不要讓走線佈線穿過分割處。電路板中最常見的電磁干擾源之一就是來自穿過分割處的走線,而它們的信號返回沒有明確的路徑。 |

|

讓數位和類比區域的電源和接地彼此分開。在接地平面被分割成類比和數位接地的情況下,只允許兩者之間有一個單點連接,以避免產生任何計畫之外的回路或天線。 |

|

讓電源平面彼此隔離。我們肯定不希望讓電源雜訊最終進入數位或類比電路。 |

|

確保在分區中留出足夠的空間來妥善設計 PDN。像 CPU 這樣的大型耗電部件需要大量的電源濾波來控制其雜訊尖峰。 |

對於 PCB 設計中的功能分區,還有其他一些需要注意的事項。要為電路板的散熱留出空間。根據放置的位置,高大的零組件 (如連接器) 可能會無意中阻擋處理器晶片等熱運行零件所需的氣流。請記住,一個分區中的熱元件可能會給下一個分區造成問題,因此要做出相應的規劃。

現在,我們已經準備好為 PCB 設計繪製分區了,那麼讓我們來看看設計工具會提供哪些幫助。

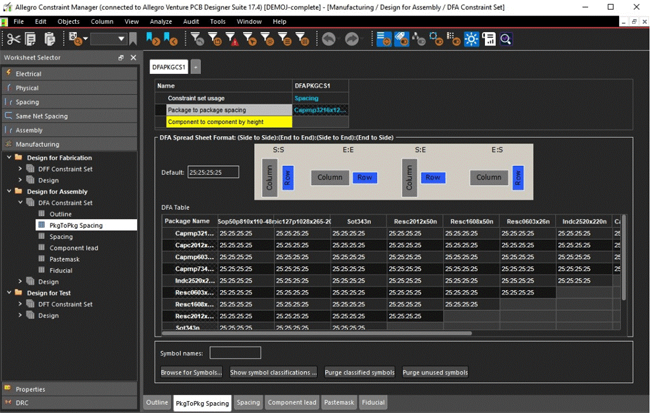

在 Cadence 的 Constraint Manager 中設置元件放置要求。

如何有效使用工具來規劃分區

PCB 設計工具 (如 Cadence® Allegro® 系列軟體) 提供了很多功能,供我們在繪製功能分區時使用。下面來列舉一些使用方法:

電路圖: |

|

當繪製電路圖時,將需要位於同一分區的零件放在一起。這不僅有助於整理電路圖,還可以使用這些電路圖分組來幫助我們選擇和整理 layout 中的零件。 |

|

「房間」 (rooms): |

|

在繪製區域圖時,將「房間」畫在設計上是很有幫助的。雖然該步驟可以透過一些簡單的圖形來完成,但 Allegro 提供的名為「rooms」的功能也可以提供幫助。在電路圖中,將使用唯一的房間名稱將房間屬性附加到一個分區的部分。在 layout 中,將使用圖形化的房間屬性創建分區,並給它也起一個名字。然後可以配置這些房間,只允許具有相應房間名稱的零件歸入房間,從而將零件分配到所有已設置為房間的分區。 |

|

約束管理器 (Constraint manager): |

|

該實用工具可輕鬆將類分配給零件和網路,以及設置層佈線約束和高速設計規則。這為 layout 設計人員提供了另一個用於整理設計資料的有用工具。 |

|

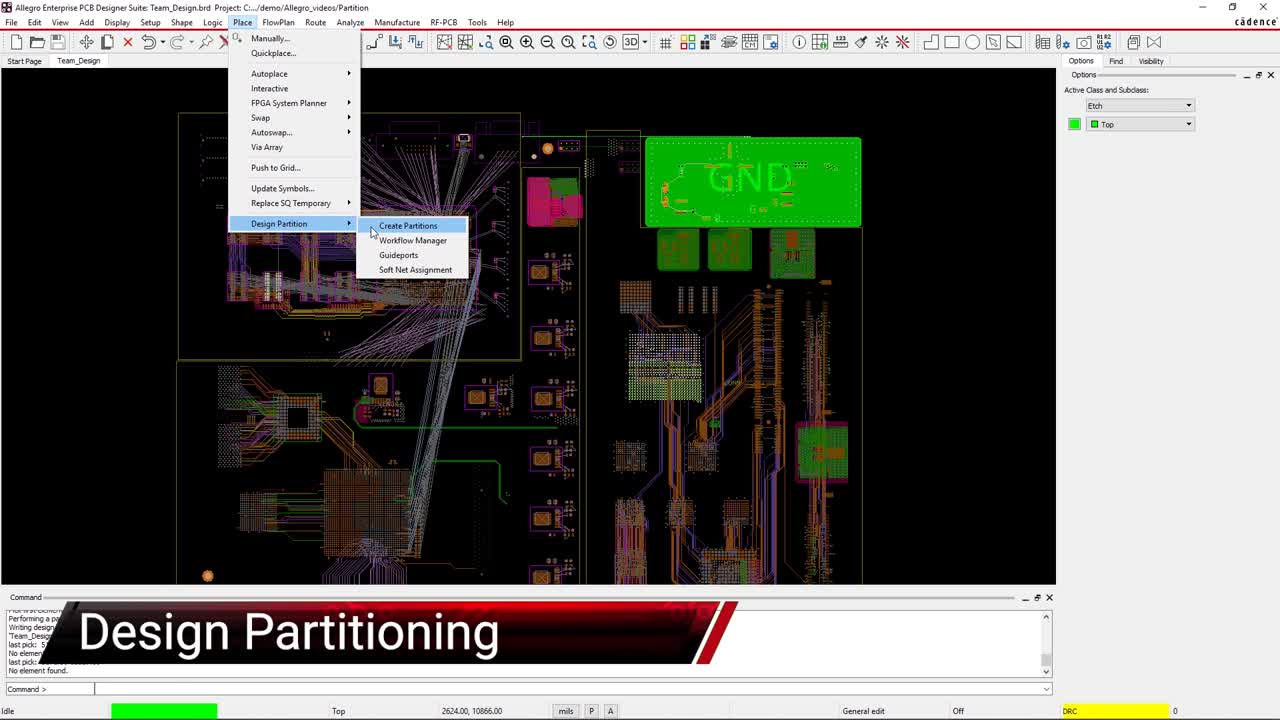

設計分區: |

|

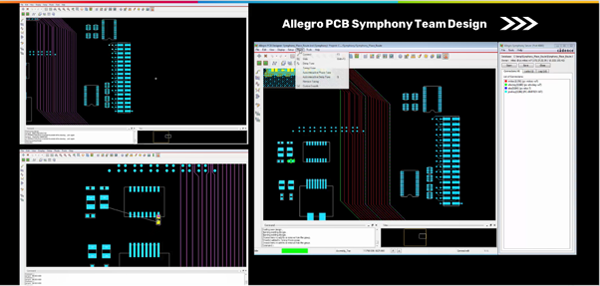

Allegro 中的這個選項允許設計人員在 layout 中指定用於團隊設計的分區。不同的設計人員可以在電路板中的不同分區上工作,然後將工作成果更新到主設計中。 |

開始放置零件之前,在 PCB 設計中設置功能分區將為我們提供成功 layout 所需的組織基礎。請試想一下,在原本靜態的分工作業模式中,需將 layout 分成數個區域交由工程師分別設計後再整合成一個完整的檔案,其中如果有衝突或是需要討論的部分就必須等到整合檔案後才能確認,非常耗時耗力,特別是在高複雜高密度的 PCB 設計上。

現在,透過 Allegro PCB Symphony Team Design 功能可讓您建立一個通用資料庫以執行線上 layout 協同作業,且每個團隊成員在執行設計時可在畫面中即時查看到其他團隊成員對 layout 所做的變更。 使用 Symphony 線上協同設計功能不只能夠在本地區域網路中建立連線專案,甚至可與遠端的工作夥伴建立連線,同步進行多人協同設計、即時確認,加速 PCB 設計流程、大幅減少返工時間。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」