By Team Sigrity, Cadence

在當今這個資料速率高達兩位元數 Gbps 時代裡,工程師的工作越來越不容易,正確地設計並表徵系統以符合不斷更新的業內標準搞得大家焦頭爛額,不僅要對高速串列鏈路及其所有損耗進行模擬,還得通過合規測試。

更要命的是,大家熟悉的依靠比較不同頻域參數 (例如插入損耗、回波損耗、串擾等) 從而發現設計缺陷的傳統合規性檢查方法已經 out 了!

由於沒有考慮到不同參數的相互依存性和權衡裕量問題,傳統方法容易導致過度設計和成本過高問題。例如,如果一個設計滿足插入損耗和串擾指標且有很大裕量,而僅有回波損耗一點點不達標時,那麼即使它實際上能夠完美運行也一樣會被視為設計上的不合規。那怎麼辦呢?

Channel Operating Margin (COM) ——通道裕量,是 IEEE802.3bj-2014 100 Gb/s 背板操作和銅纜乙太網標準中介紹的合規性檢查方法。作為時域規範,其定義如下:

COM = 20 log10(As/Ani)

其中,As 和 Ani 是指接收器輸出端的信號和雜訊幅值,並考慮整個端對端通道特性 (包括發射器 (TX)、接收器 (RX) 和通道損耗) 的影響。

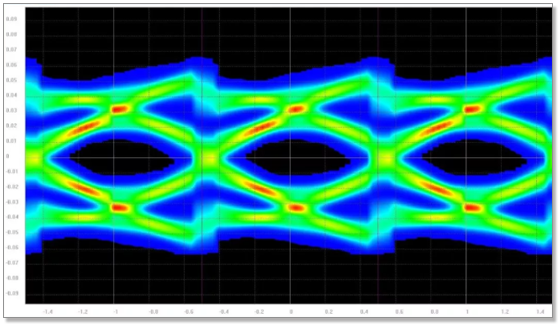

As 由通道中的 s 參數計算出來,包括近端和遠端的串擾路徑、TX 和 RX 器件封裝模型、TX FFE 和 RXCTLE 濾波器、TX 和 RX 輸出 / 輸入阻抗模型、以及 RX DFE 模型。相對於來源於發射器、均衡後的殘餘 ISI、抖動 (轉換為幅度雜訊) 、峰值串擾的雜訊與 COM 指定的 RX 雜訊濾波器級聯的 CTLE 雜訊,由於 FFE、CTLE 和 DFE 的均衡抽頭都實現了優化,As 也相應實現了最大化。

雜訊幅度 Ani 是在假設為高斯雜訊分佈的情況下,根據傳播到接收器輸出端的所有噪音源的組合分佈函數來計算的,並通過將累積分佈函數等同於檢測器誤差率 (DER0) 來求解,以使得到的雜訊電平對應於該統計誤差率。當 COM 值超過某個閾值,如 IEEE802.3bj 標準中的 3dB,即滿足設計合規性要求。值得一提的是,COM 是由許多相互關聯的信號變數組成的,因而工程師才能在滿足 BER 或 DER0 要求的前提下進行設計權衡。

JCOM 是針對 JEDEC JESD204C C 類實體層規範的合規性方法,用於將資料轉換器 (ADC 和 DAC) 連接到邏輯器件 (如 ASIC、FPGA 等) 的高速串列鏈路 (資料速率範圍從 6.375 Gbps 到 32 Gbps) 。

JCOM = 20 log10(As/Ani)

與 COM 一樣,JCOM 也是在接收器輸出端計算信噪比 (SNR) 的時域測量值,並允許設計人員靈活管理鏈路中 TX、RX 和通道損耗之間的權衡。它包含對 COM 的幾種改進,比如定制化器件封裝模型以及頻率相關的 TX/RX 輸出 / 輸入阻抗模型。當 JCOM 值大於閾值 2dB 時,設計即滿足合規性要求。

那麼,使用 COM 或 JCOM 將對我們的工作有何益處? 主要有以下三點:

1. |

在通道損耗、串擾、發射器和接收器指標之間進行設計權衡,以避免過度設計和成本增加 |

|---|---|

2. |

一旦獲得考慮串擾因素的通道 S 參數,可直接、迅速地確認設計是否滿足合規性要求 |

3. |

可使用 COM / JCOM 來?明確定系統架構設計中的決策問題,例如 FFE、CTLE、DFE 配置和均衡抽頭數 |

COM / JCOM 可說明我們以更快速、高效的方式通過合規性檢查、並減少過度設計,這對於今後的高速串列鏈路設計至關重要。Cadence 的 Sigrity™ SystemSI™ 現已包含 COM 通道合規性功能,可幫助工程師快速便捷地判斷系統設計是否滿足要求。JCOM 通道合規性功能將於不久後問世,敬請期待。

如果您正在被通道合規性模擬問題所困擾,請聯繫 Cadence 授權代理商 映陽科技,我們將運用 SystemSI 的 COM 通道合規性技術快速解決您的煩惱。

了解更多關於 Sigrity System SI

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」