By Team Sigrity, Cadence

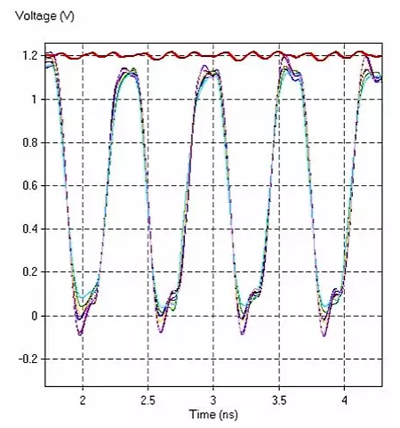

同步開關輸出 (SSO) 引起的同步開關雜訊 (SSN) 一直是信號完整性 (SI) 領域幾十年來的熱門話題 (見下圖)。一些人認為只有使用電晶體級模型的 SPICE 模擬才能提供 DDR4 等記憶體介面所需的精度,以模擬在位址和資料匯流排上同時驅動多個信號。而即使使用 SPICE 模擬器和電晶體級模型,互連模型也需要包括信號、電源和地之間相互作用的細節。有些人認為這種模型只能使用向量網路分析 (VNA) 從物理測試平臺中提取。但是,如果您用一塊生產好的 PCB 來執行物理模型提取,那麼您已經處於產品開發週期晚期了,而大多數設計團隊都希望在設計週期的早期進行這些模擬,以?明優化電源分配網路、信號佈線和記憶體控制器選擇。

Cadence® Sigrity™ 團隊一直在推廣兼顧電源的信號完整性分析方法。現在,Cadence 又有了一些新的成果。然而,在進一步討論之前,您可能需要花一些時間來閱讀白皮書「 應對『兼顧電源』挑戰的記憶體介面設計 」,從而瞭解一下我們的流程。

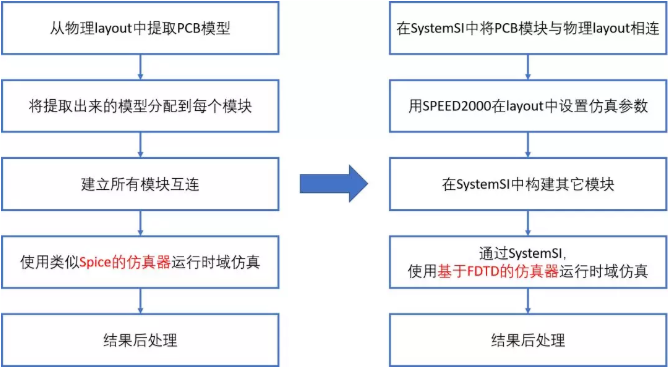

這篇白皮書回顧了兼顧電源的信號完整性分析流程,該流程提取了系統的互連模型(如封裝模型、PCB 模型、連接器模型等),然後將它們與 IBIS(5.0+)器件模型級聯,組成時域模擬系統。Sigrity SystemSI™ 多年來一直支援這種流程:它使用 Sigrity 提取工具從物理 layout 中提取 PCB / 封裝模型,再將模型分配到各個模組以連接每個模組的信號、電源和地,然後使用類似 SPICE 的模擬器來運行時域模擬以生成用於後處理的波形。透過提取出的包含電源網路的互連模型、將適當的電源引腳從驅動緩衝器連接到接收緩衝器、以及在時域模擬中使用兼顧電源的 IBIS 模型,就能模擬出包含電源網路的非理想供電效應的信號完整性結果。

圖:原模擬流程

只要時域模擬器可以處理大型、複雜的系統級模擬,並且所有模型都被正確提取,以及連接電源接地引腳的返回電流路徑也是正確的,那麼該流程就可以正常工作。

不幸的是,互連模型的龐大規模(即 S 參數)會導致模擬時間過長。當信號和電源網路一起被提取用於平行匯流排設計時,電路板和封裝的 S 參數會有數百個埠。假如 S 參數模型在 DC 上沒有資訊,那麼當 S 參數模型在低頻範圍內的表現不佳時,時域模擬便會遇到收斂問題。

另外,當設計團隊從這種類型的模擬中獲得結果時,他們還會面臨調試設計問題的挑戰:因為一旦封裝和電路板模型被提取,layout 中的所有物理資訊都會丟失。因此,如果 SI 工程師想要糾正系統時域模擬方面的問題,他們就不得不重新回到layout 進行更改,並再次提取模型。顯然,這對於「what-if」分析並不理想。

我們能否擁有一種兼顧電源的信號完整性模擬流程,避免使用模型提取並降低時域模擬收斂失敗的可能性呢?答案是肯定的。現在 Sigrity SystemSI 和 SPEED 2000可以協同工作,使這一設想對於 SI 工程師而言成為可能。在 Sigrity 新的工作流程中,SystemSI 不再從 layout 中提取模型,而是採用新模組直接連接到電路板或封裝 layout 的方式。一旦啟用流程,使用混合求解器的 FDTD 模擬將直接在後臺的 SPEED 2000 中執行(見下圖)。模擬完成後,模擬結果將返回到 SystemSI 以進行後處理和測量。對使用者而言,介面和設置過程與使用提取模型的流程相同。

圖:原模擬流程 → 新模擬流程

這兩個流程的關鍵區別在於,新流程不是使用類似 SPICE 的模擬器,而是使用混合求解器的 FDTD 方法進行時域模擬。

該流程使設計團隊能夠透過直接訪問封裝或電路板 layout 來執行「what-if」分析,降低互連模型的複雜性,並使時域模擬收斂問題得到解決。

現在,您可能想知道我們白皮書中討論的方法是否已經不再需要。也不盡然。如果您在設計週期晚期,並且有一些 VNA 提取的模型,那麼這是使用基於模組的互連模型方法的絕佳時機。但是,如果您仍處於設計驗證階段,有權訪問 layout 並期望進行修改,那麼直接的 FDTD 模擬方法可能會是更好的選擇。

有關基於 FDTD 的兼顧電源的信號完整性模擬的更多資訊,歡迎查看我們的 Sigrity技術小幫手:如何輕鬆實現DDR介面精準分析而無需處理大型S參數 (中文Demo)。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」