By Cadence

本文要點

射頻天線有多種形式,從整合在晶片中的扁平天線,到直接印製在 PCB 上的銅質天線。 |

|

創建帶有一個或多個天線的版圖時,需要確保在 PCB 不同電路模組之間彼此隔離。 |

|

在設計一個射頻天線時,應該使用 CAD 工具,此類工具可以説明設計隔離結構、過渡結構,甚至可以為 PCB 設計印製天線。 |

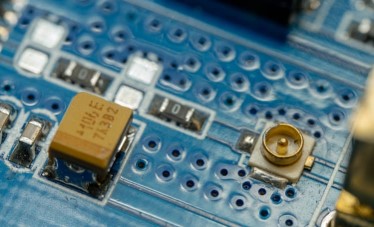

圖中的 SMA 連接器與射頻天線之間具有同軸連接。

如今,很難想像有哪種消費電子產品不包含天線,甚至連車庫門開啟器也可以透過藍牙或 WiFi 與手機相連。每當有新的射頻天線添加到 PCB 版圖中,都會給射頻設計師帶來新的難題,特別是當前的設計又開始重視起模擬設計技能。隨著諸多射頻功能被添加到新的 PCB 上,設計師該如何確保系統中的信號不被破壞,並保持信號完整性呢?

一些簡單的設計選擇可以確保射頻信號不被附近的數位元器件所削弱,同時也將有助於防止多個類比信號之間發生相互干擾。雖然在設計混合信號或全射頻系統時,需要考慮很多射頻設計方面的問題,但天線設計和版圖可能是最重要的兩個方面。下面我們瞭解一下 PCB 版圖中的射頻天線設計以及如何確保類比信號完整性。

射頻天線設計基礎知識

在設計定制天線或選擇 COTS 天線用於射頻 PCB 時,需要遵循幾個基本要點。所有射頻天線都有一些特殊的特性,在設計階段應予以考慮。每根天線都需要具備以下元件:

浮動的導電輻射器: |

|

用於發出輻射的天線單元。 |

|

參考平面: |

|

天線的參考平面或單元有助於確定天線結構在每種天線模式中的方向性。 |

|

饋線 (Feedline): |

|

饋線用於將輸入信號從射頻元件輸送到輻射天線單元中。 |

|

阻抗匹配網路: |

|

天線通常具有約 10 歐姆的阻抗,因此需要與饋線阻抗相匹配,以防止反射並確保在所需的載波頻率和頻寬下實現最大功率傳輸。 |

許多標準的天線設計已經得到充分研究。我們可以在網上找到許多參考設計,然後可以將其複製到自己的 PCB 版圖中。我們還可以在微波工程教科書中找到許多標準天線結構的設計公式。最後,如果想使用 COTS 射頻天線,可以在市場上找到許多價格低廉的設計。無論選擇使用哪種射頻天線,都需要在版圖中仔細放置,以防止電路板各個部位之間發生干擾。

射頻天線版圖技巧

設計好天線之後,需要判斷應該把它放在 PCB 上的什麼位置。射頻設計師可從混合信號設計師那裡獲得一些技巧 (大多數射頻電路板實際上是混合信號電路板),以防止射頻前端、後端和數位部分之間出現干擾。

高效輻射: |

|

旨在確保來自天線單元的輻射離開電路板,而不被 PCB 版圖中的其他結構所接收。 |

|

隔離: |

|

同樣,我們也不希望 PCB 版圖中的多個部分直接發生相互干擾。 |

|

電磁相容性 (EMC): |

|

最後,需要確保版圖不會接收來自其他設備的信號,這些設備可能在廣泛的頻率範圍內發射信號。 |

在 PCB 的實際設計中,大多數設計目標都是相互競爭的,但有兩個要點需要遵循,這將有助於平衡這些設計目標。

在 PCB 版圖中讓電路模組彼此分開

這是一個基本的混合信號 PCB 設計要點,也同樣適用於射頻天線的版圖。需要將天線部分放置在電路板上,並與其他電路模組分開。一般來說,最好是將天線部分放在靠近電路板邊緣的位置,並遠離其他模擬元件。這樣可以將強輻射限制在電路板上的一個位置,並確保各個部分之間的干擾最小。

PCB 上的網格化系統版圖

網格化的挑戰在於確保不同部分的回流路徑不會相互干擾,否則將導致雜訊耦合和串擾。使用整合在先進 PCB 設計工具中的場求解器,將有助於在創建版圖時發現回流路徑的偏差。對於高頻設計,要採用連續的接地平面結構,以確保一致的回流路徑。

隔離天線部分

現代手機和高速資料網路設備採用了創造性的隔離結構,這已成為射頻隔離技術的黃金標準。很簡單,隔離就是在電路板上的射頻敏感元件周圍放置一些遮罩物,以阻止發射器和接收器之間的電波傳播。下面的表格中介紹了可以用於射頻天線部分的一些結構,以隔離元件、饋線和天線,或隔離外部噪音源。

隔離結構 |

優點 |

缺點 |

|---|---|---|

屏蔽 |

只要結構中的縫隙足夠小,隔離度就很高。 |

可能較為笨重,或者需要定制。 |

過孔柵欄 |

與接地灌銅的效果相似,但佔據的電路板空間更少。 |

隔離度較低,只支援窄帶,截止頻率低。 |

接地灌銅 |

用於射頻天線饋線,可創建一個具有高隔離度的共面波導。 |

佔用電路板空間,在元件排列密集的小型電路板上不是很理想。 |

波導佈線 |

具有非常高的隔離度,可以進行模式選擇,以實現特定頻寬的佈線。 |

佔用電路板空間,只適合用於最關鍵的線路。 |

帶隙結構 |

可以為特定的頻寬提供中到高的隔離度。 |

非常適合高頻應用,佔用的電路板空間較少。 |

隔離結構通常放置在射頻元件之間,以阻止它們之間的雜訊耦合和功率交換。確定使用哪種隔離結構來確保射頻天線信號的完整性,是一個複雜的設計問題,業界對此已經進行了深入的研究。如果我們不是橢圓積分方面的專家,就需要依靠電磁 (EM) 場求解器來確定這些結構如何影響饋線 / 射頻天線的阻抗,以及這些結構提供的隔離水準。

如果使用電磁場求解器,就可以使用近場和遠場模擬來確定 PCB 版圖中出現強輻射的區域。一旦確定了這些區域以及發射的頻率,將有助於確定應該使用哪種類型的隔離策略。最好是直接使用頻域 (FDFD 方法),而不是使用傅立葉 (Fourier) 變換來轉換 FDTD 結果。

射頻天線設計和版圖創建需要格外注意細節,因此多加謹慎是有意義的,從而確保射頻設計的隔離和信號完整性。

想要實現射頻天線版圖創建和信號完整性分析的一體化設計嗎?

Cadence AWR Design Environment® 新版本 V16 具有跨平臺的工作流程,支援基於 Virtuoso® (晶片) 和 Allegro® (PCB / 封裝) 平臺的射頻到毫米波設計,並與系統級分析解決方案 Clarity™ 3D Solver 和 Celsius™ Thermal Solver 整合。

新版 AWR Design Environment,包括 Microwave Office® 電路設計軟體,使客戶能夠為汽車、雷達系統、5G 等應用設計互聯系統。與同類競品的工作流程相比,AWR 緊密整合的平臺可以將周轉時間加速高達 50%,其射頻整合水準在業內也是首屈一指。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」