隨著電晶體製程比例的縮減越來越接近物理極限,越來越多的公司把發展戰略從矽轉向有高級封裝工藝的多晶片設計,以保持自身在電子行業的創新和快速發展能力。高級封裝,在技術、材料及工藝上展現了巨大的進步;與傳統系統級晶片相比,高級封裝能夠順利高效地生產出高性能、高良率的複雜系統,且具有很大的成本優勢。

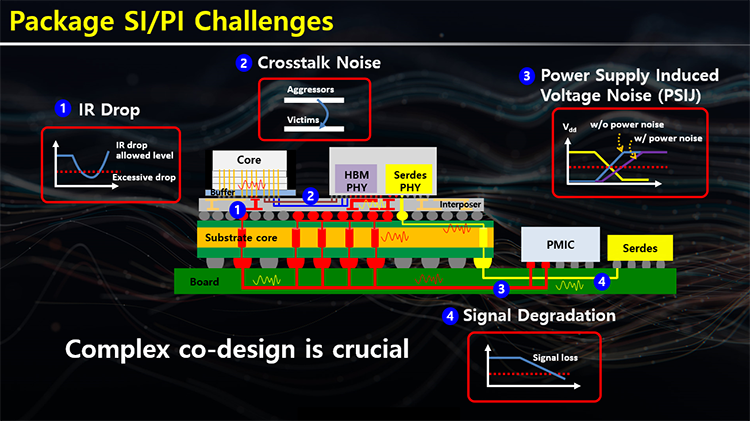

圖 1:訊號完整性 / 電源完整性設計挑戰一覽;

來源:Samsung Foundry

雖然複雜、高性能的高級封裝具有很高的優越性,但由於積體電路傳送速率快、電源電壓低、電路處理性能要求高等問題,工程師們也同樣面臨著訊號完整性(SI)與電源完整性(PI)的難題。比如在高頻寬記憶體中(HBM)、 高速平行介面(HPI)與高速序列介面(HSI)的訊號完整性解決方案不盡相同。此時經認證的參考流程則顯得格外重要,尤其當工程師需要將交流和直流電源完整性需求都考慮在內時,如果該設計沒有遵循經認證的參考流程,那麼貿然簽發這一高級封裝設計則是鋌而走險的。

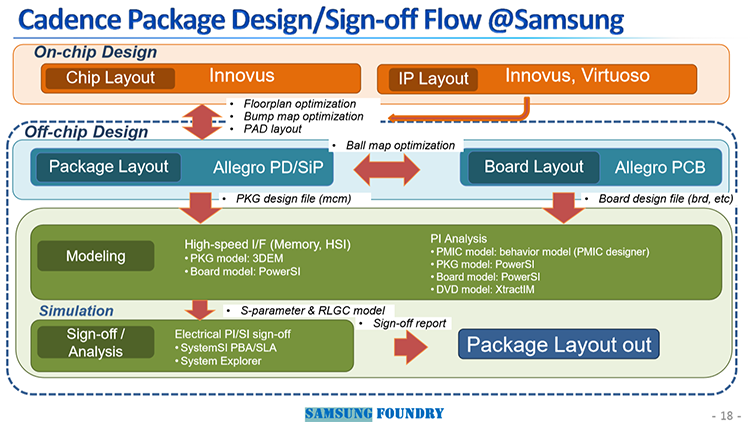

圖 2: Cadence 封裝設計及簽發流程;

來源:Samsung Foundry

去年,Cadence 與 Samsung Foundry 合作,為其客戶發佈了業內首個高級封裝參考流程。在今年矽谷的 CDNLive 大會上(CDNLive2019-SV),Samsung Foundry 的 Sylvie Kadivar 博士和 Max Min 博士介紹了高級封裝設計和簽發參考流程的詳細資訊,覆蓋了各種高速平行介面(HPI)、高速序列介面(HSI)等訊號完整性的模擬需求,以及交流、直流的電源完整性模擬需求。

完整的 Cadence 高級封裝流程獲得 Samsung 認證並與其獨家黃金流程相關聯,該高級封裝流程運用 Cadence 的 Allegro® 技術、Sigrity™ 技術、Voltus™ 技術和 Spectre™ 技術, 透過基於 FO-PLP 和 2.5D 矽仲介層封裝的測試用例,獲得了記憶體介面、高速介面,CPU / GPU 的核心電源分配網路的驗證審核。

相關論文亦由 Samsung Foundry 的 Sungwook Moon 博士與今年年初在 DesignCon 展會(DesignCon2019)上發表。

藉助高級封裝參考流程,Cadence 和 Samsung 的共同客戶現在擁有了一個經驗證的步驟化的方法來證明並有信心的簽發他們的高級封裝設計,使設計的首次成功成為可能。

本文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」