By John Park, Cadence

當下,許多類比、射頻和混合信號設計都需要在不同的襯底技術中集成多個 IC 以實現所需的性能目標。鑒於當今晶片、封裝和電路板的複雜性,不僅矽,包括其他非矽材料都需要被用在設計中以達到最優的系統性能。異構器件的集成使得設計人員能夠實現用單片 IC(SoC) 設計方法無法輕易複製的設計結果。然而,異構集成也為設計人員帶來了全新的挑戰。

今天,在「系統級」 (IC-封裝-PCB) 進行設計,會涉及到大量關於下游封裝 / PCB 對晶片性能和可靠性影響的經驗猜測。 傳統上,模擬 / 射頻 IC 設計人員只需模擬 IC 而無需考慮封裝和 PCB 的影響。 然而通常來講,封裝包含一個或多個 IC 和互連元件,有時也可能包含 IC 工作所需的分立元件;同樣地,PCB 也包含多個封裝、互連和分立元件。 因而,將整個系統統一起來進行模擬,對捕捉高頻性能是非常重要的。由於 IC 設計和封裝設計人員使用不同的原理圖輸入工具,IC 設計人員不得不重新捕獲封裝系統原理圖並放置于 IC 原理圖的測試平臺上,才能夠對聯合系統進行模擬。

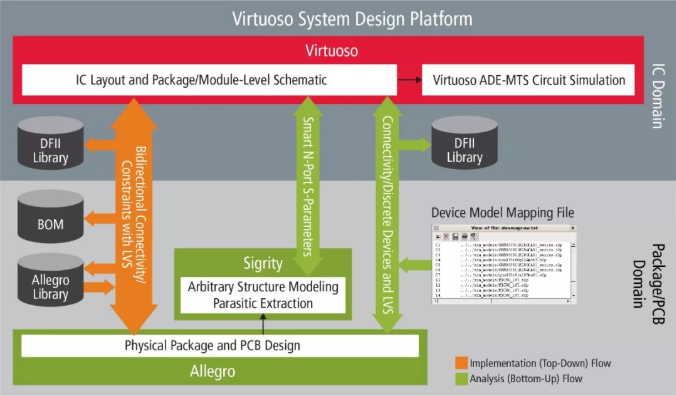

為了在早期設計階段和流片之前識別並消除潛在誤差,建立一個緊密的設計和模擬環境從而幫助 IC 設計人員在整個 PCB、封裝系統和寄生效應的情景下實現 IC 的自動模擬是十分必要的 。我們已有一個相似的設計環境可以對數字 IC 的 I/O 與 I/O 互連進行模擬,現在,Virtuoso System Design Platform 又使在包含寄生參數的完整 PCB / 封裝電路中對類比 / 射頻 IC 進行模擬成為了可能,最大限度地減少了設計反覆運算次數。

圖 1:Virtuoso 系統設計平臺

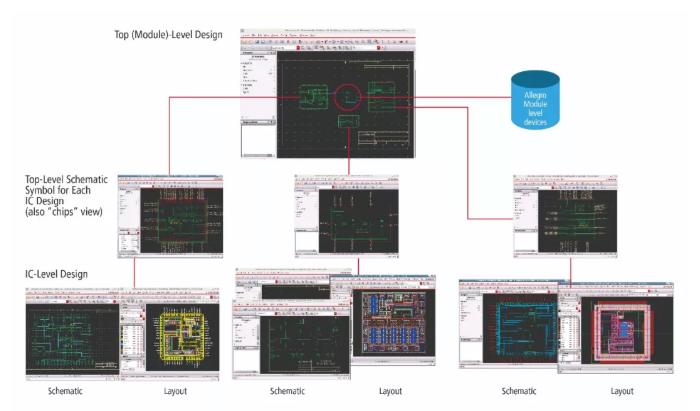

此流程提供了通過單個原理圖編輯器,驅動 IC 和封裝 layout 的能力。 通過使用同一原理圖編輯器 (Virtuoso Schematic Editor),IC 設計人員可以在一個通用的環境中更好地進行系統級設計,包括預佈線系統模擬 (IC 和封裝一起),繼而驅動各自領域的佈線。該流程還通過生成 Cadence SiP Layout 中使用的晶片引腳使大部分封裝級庫的開發流程自動化。

晶片與封裝之間的協同設計

高階使用者可以在晶片與封裝之間協同設計,以實現更好的封裝級佈線和 / 或引線鍵合。該流程可以讓設計人員在封裝佈局佈線之前將封裝的原理圖放入 Virtuoso Schematic Editor 中進行設計。 進一步則可以從 Virtuoso Layout 套件中匯出晶片引腳和符號,並利用它們進行封裝原理圖構建。 資料的雙向流動可將原理圖中所做的編輯動態地傳遞到 SiP Layout,反之亦然。 設計人員還可以生成物料清單,以直觀的方式視覺化設計差異,並使用此流程查看 layout 報告。

圖 2:RS Pro Evikey

一旦封裝或 PCB 被該流程設計完畢,基於分析的該流程將會被帶入完整的模擬環境中,不需要對 PCB或封裝以及電磁模擬領域有專業認知也可以輕鬆完成。 這種方法將會顯著提高生產力。此分析流程允許 IC 設計人員將 PCB 和封裝 layout 及其相應的寄生模型 (以 S 參數或 SPICE 表示) 導入 IC 設計環境,進而對 PCB 或封裝連接進行讀取,並創建一個包含寄生模型的原理圖。該原理圖可以隨時在 PCB 或封裝系統的環境中進行模擬。

該設計平臺有助於在包含封裝 / PCB 互聯和外部元件的條件下對 IC 進行集成和模擬。 由於 IC、封裝和 PCB 通常由不同的團隊在不同地理位置使用不同的設計工具進行設計,並且在設計週期的不同階段都各自獨立,因此該設計平臺尤為重要。該平臺將封裝和 PCB 級 layout 寄生效應共同納入通用原理圖中,實現了整個系統的跨區域模擬。這有助於在流片前確定關鍵的性能偏差。

然後,所需修改資訊可以直接被傳遞給封裝 / PCB團隊。 這裡有一個重要功能,即是可以智慧地將寄生模型融合到模擬原理圖中。如果模型中還包含分立器件,那麼它們則會在創建模擬電路圖時被自動濾除掉,從而不會在模擬中被重複計算。 自動濾除需要重新調整介面,以確保正確融合並去除所有 SMD 以避免冗餘。

擁有這樣一個強大的集成平臺可以為設計人員帶來以下三大優勢:

通過使用通用的原理圖編輯器,設計人員現在可以為封裝的 layout 設計原理圖。Virtuoso Schematic Editor 是可以驅動 IC 和封裝設計的統一的原理圖編輯器。 |

|

設計人員可以創建封裝或 PCB 帶寄生效應的原理圖,並利用 Virtuoso Analog Design Environment 進行模擬,其中包含的多重技術模擬是實現完整的系統模擬的重要機制。 |

|

設計人員可以同時通過協同設計晶片簡要流程來設計 IC 和封裝 layout,最大限度地減少設計反覆運算次數並減少後期的佈局規劃和設計可行性問題。 |

簡而言之,Virtuoso System Design Platform 是一個全面的、基於系統的解決方案,實現由單一原理圖驅動的 IC 和封裝的模擬以及 LVS 檢查。

該設計平臺在 2017 年榮獲 Electronic Products 網站評選的年度電子產品大獎。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」