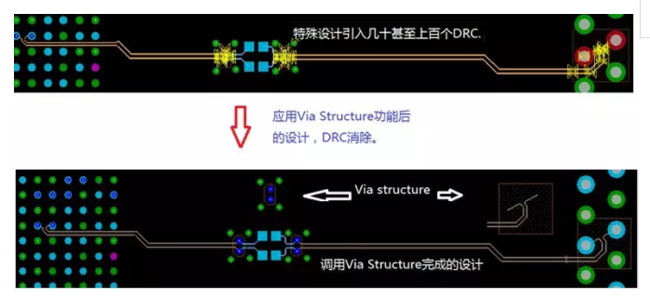

隨著 PCB 上高速訊號速率的提升,高速設計方案會在 PCB 設計中引入比較多的 DRC,最常見的是 K/L、K/V 等 DRC。設計者允許這些 DRC 的存在,但是這些 DRC 的占比已經超過整板 DRC 的 50% 以上,他們的存在會降低 ALLEGRO 的運行速度,甚至延長某些操作的執行時間(例如:更新 DRC、Database check等),還影響投板前的 DRC 排查效率和品質。Allegro17.2 的 Via structure 功能,可以幫助設計者去除這些 DRC,提升設計效率和設計品質。

步驟一:根據需求創建 Via structure

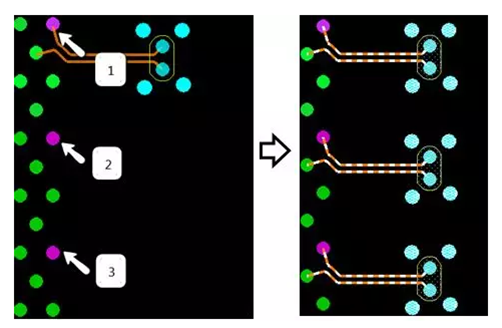

設計者可以根據需求,創建不同的 Via structure,Via structure 可以包含您所需要的設計物件,例如 Via、Shape(包括 RKO)、Cline 等。Via structure 的創建方法很簡單,找到如下的命令,按照 Command 欄的提示即可順利完成。下面舉一些我們已有的例子,僅用於說明使用方法。

1. |

晶片側的 Via structure 範例,Via structure 可以只是 Cline,也可以是 Via、shape、Cline 的合成體。 |

|---|

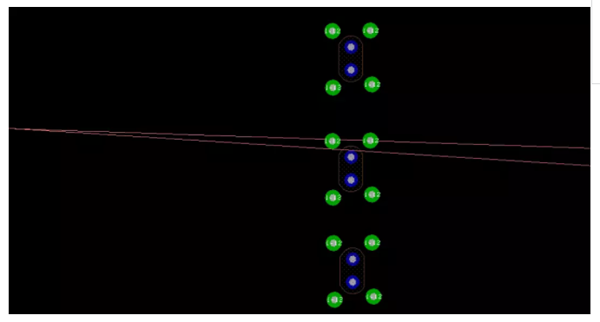

2. |

高速佈線層切換的 Via structure 範例。 |

|---|

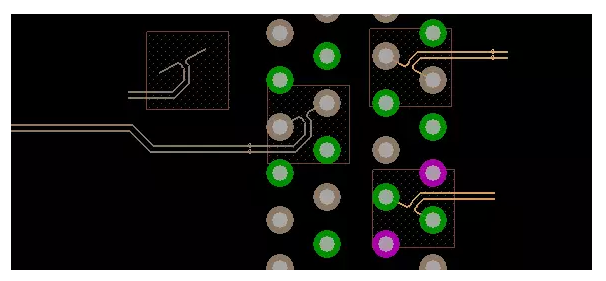

3. |

連接器側的 Via structure 範例。可以只包含 Cline 和您所需的其他物件。 |

|---|

步驟二:在設計中調用 Via structure

Via structure 定義完成後,我們可以在設計中直接調用,然後將其連接起來,即可完成高速鏈路的佈線。如下的實例中,應用上面提到的幾個 Via structure 範例,完成了一個高速鏈路的設計。設計完成後,K/L、K/V 等報錯不再出現,設計變得更加有效,更有利於提升設計品質。

Allegro 的 Via structure 功能,可以幫助設計者消除 PCB 上為了落實設計需求而引入的合理的 DRC。讓設計更加高效、高品質,且可以促進高速訊號設計的一致性(每次遇到同類設計,都可以直接調用已有的範本)。

文章授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」