设计更便利,工作有效率!

当我们使用 EDA 工具时,有些比较常用的动作或指令可能会随着不同的区域或习惯而有着些许程度上的差异,所以 Allegro / OrCAD PCB 和 APD / SiP 提供了撰写插件的 Skill,外挂在程序上以提高方便性。而新版的 OrCAD X Capture / CIS 也在 V16.5 之后提供了 Tcl / tk 让我们可通过撰写的程序,外挂在 Capture / CIS 上让设计更便利,工作上更有效率。

Graser 将一些较常用的功能设计成 GrasereWARE 系列并整理成三组程序:

FrontendPack

针对电子工程师在绘制线路图的需求,挂载在 Capture / CIS 上,使 OrCAD X Capture / CIS 的操作更加便利。

EnhancePack

针对 PCB 设计工程师设计布线时的需求,应用在 Allegro / OrCAD PCB 程序上。主要含括整个 PCB Layout 流程的前、中、后三阶段。

PackagePack

因应 Package 封装设计的特殊需求,挂载在 APD / SiP 程序上,希望让您在封装设计上能更加便利。

( APD / SiP 的使用者也可同时挂载 EnhancePack )

OrCAD X Capture / CIS 操作更便利

1. Capture Design Compare

在 Capture 的软件中,针对修改完成的线路图,可以跟前一版备份的线路图做零件及联机关系的比对,并且在比对完之后,可通过简单的显示接口,了解到两份原理图之中的零件或 Net 差异。

2. NC-Part

用户能在表格式的列表中很快的找到并定义不插件零件,并且宣告设定 NC-Part 后在图面的零件颜色变化更加强了原理图零件可多选设定功能;在 BOM 表的输出上能做自动区隔标准零件与不插件零件的定义。可设定以搭配 V16.6 BOM_IGNORE=TRUE 的属性使用。

3. Replace BUS Alias

以往 OrCAD X Capture 使用者的必须个别编辑修改这些 BUS net 名称,以达到重新命名宣告之动作。Replace BUS Alias 程序是希望用户能够快速的搜寻并且取代成新命名的 BUS net 名称,并且可以依照 Replace by select / page / design 不同的模式下做的操作。

4. Import / Export Properties

轻松的将 Capture 线路图中的 Part、Part Pin、Flat Net 的属性 Export 成 Excel File,也可利用 Import 功能更新至线路图中。利用其完整的接口、便利的字段设定,可配合 Excel 对 OrCAD 线路图上的属性字段做大规模的截取或刷新动作。

5. OCC2INST

原理图为平坦式或简单的阶层式电路设计时,原理图属性应该只有白色属性且原理图 Mode 为 Instance。但有时候原理图却出现白黄属性,Mode 却为 Occurrences,当出现此状况其白黄属性值有可能不同;目前 Capture / CIS 程序所提供的 ”Transfer Occ. Prop. to Instance” 程序只能针对 PCB Footprint 与 Reference 零件属性字段做同步。 OCC2INST 程序是当 Capture 要做 occurrences transfer to instance mode 时,让使用者可以自定义 Occurrences 同步到 Instance 的属性字段。

6. Reference Edit

Modify RefDes (图1)

OrCAD X Capture 原理图零件 Reference 常会因为摆放位置或是连接的模块,需要在标准的 Reference Prefix 前方或后方增加特殊的字符定义,如 CE,CP,BC 等状况,但通常这种状况需要 Capture 使用者自行手动一颗一颗零件编辑 Reference 属性。Reference Edit “Modify RefDes” 功能,就是针对这种状况,可以在线路图 Page 中,将零件选取或对 Page 所有零件或对整个 Design 的 Reference Prefix 做变化设定。

Annotate RefDes (图2)

OrCAD X Capture 原理图零件 Reference 在做序号的编辑时,有时 Capture 用户需要一找原理图模块方块或是依照 Page 顺序做特殊编码,可对 Design or Signal Page 中的所有零件设定字符串或针对原理图 Page 中所框选的零件做特殊编辑。

(图1)

(图2)

7. Graser Allegro Netlist

用 3rd party 的方式由 OrCAD 转出联机关系档,可供 Allegro / OrCAD PCB 以 Other 方式加载联机关系之外,并可传递如线宽或锁定等特殊属性。

让 Layout 设计更便利

以 PCB 的设计流程区分成以下部分

PCB Layout 前的零件库数据建立、环境设定与限制区设置

1. Create Special Pad Shape

Allegro 对于 Pad 形状只提供圆形、正方形、长方形、长圆形 (Oval) 以及八边形等几个特定图形,对于复杂一点的图形需花费较多时间去创建或从其他作图软件产出图形后再转入 Allegro。本程序提供一些常用 Shape 图形的绘制,对零件建立者而言方便许多。

2. Cut Off Silkscreen

在建立零件 Package symbol 或 Mechanical symbol 时,Silkscreen 层面上的图形必须要避开 pad 或 pad 的 soldermask 一定距离,因此在建图时就要算好避开的位置,此动作比较麻烦,而本程序让用户只要画出整条线,经由本命令,可以很快地切断 silkscreen 图形线。

3. Board Outline

本功能主要是提供用户可以在 Board file 中由单一操作接口的执行来快速建置相关的版框数据及限制区。

选定一个板子外框图,程序自动依照所设置的各项与板边距离之要求,完成各种图形,包含 Route keepin、Package keepin、Testprobe keepout。其中 Package keepin 与 Testprobe keepout 还可依照上下左右与板边不同距离之设定。

4. Board Void

选定一个或数个板内挖空图,程序自动依照所设置的各项与挖空边距离之要求,完成各种图形,包含 Route keepout、Testprobe keepout 与负片层之铜箔避开图 (antietch line)。

5. Scale Shape

本命令让用户针对板子上选到的各个 Shape 物件做放大或缩小。

PCB Layout 过程中的物件查询与修改

1. Place by Sheet No

本程序是依照线路图 (Schematic) 上各页 (sheet) 的 Part symbol 符号位置来摆放零件 (一般称为分页) ,当 Layout 工程师在进行零件摆置 (placement) 时,能够很方便地找到与某零件相关连接之其他零件,因此可以更快速地做 placement 动作。无论是 Capture 或 Concept HDL 作 Netin 都行。

2. Flip Design

把 Board file 整个设计作翻面 (Flip)。

3. No Probe by Component Height

本程序是让用户很方便地由零件高度来设置测试点避开区。

4. Pad Escape Cline Width

在走线时,如果 Net 所定的 Constraint 的 Minimum Line Width 比 Pad 还要宽时,可以很方便地从 Pin 走线时,将线宽改成与 Pad 一样宽度,走一小段之后,又可以快速地变回原订线宽。

5. Cline Cut

方便 Layout 人员在需要截断 Cline 时,可直接框选就进行裁剪的操作,比标准指令操作上省却许多步骤,且可一次切割多条 Cline,分成以线切断或以区域切断两种。

6. Pin / Pin Length Report

本程序报告用户所选 Net 所有接线的顺序数据以及每对 Pin Pair 接线长度。

7. Cline Length

可让 Layout 人员在图面上直接查询单条或多条 Cline 的走线长度。

8. Clinesegs Pair length

用户仅需选取前后两线段,程序算出包含中间所有线段长度。

9. Tune 10 Degree lines

提供快速方便的 10 度线调线功能。

本功能提供以比例方式或角度对应方式的调线功能及 undo 作业,用户可自定义折线的线段长度或起折的方向。

10. Mirror Cline at Same Layer

让用户将选到的物件 (包括 Cline 线段、零件 Symbol 以及 Via) 再依据指定的对称线作这些物件之位置 mirror 动作,放在相同层面,Symbol 以及 Via 不作反面放置。

11. Setup Testprep

让使用者很方便地设置 Net 是否需要加测试点以及测试点数量。

12. TrueType Text Shape

让用户可以将计算机系统上的 TrueType 字型写到 Allegro 上,生成的文字为 Shape 图形或以直线描边的图形。

13. Art Text

本程序是以 Allegro 本身的文字字型再做一些变化,例如斜体字、反白字、空心字、立体字,方便使用者应用于 board file 上。

14. Gold Plating

依照用户所选 mask 防焊层面,对该 mask 范围中 Top 或 Bottom 金属层所露出的 Pin、Via、Etch 物件自动生成所需镀金的 shape 范围图形。

PCB Layout 完成后总检查,资料统计与输出相关链接程序

1. Void Distance Check

让用户针对板子上各个 ETCH 层面 shape 物件内的 Void 之间的最小间距做检查与报告,并且检查两 shape 间距。

2. Minimum Spacing Check

Board file 上如果没有与 spacing 相关的 DRC 违规,我们仍然无法知道某 Net 在各层走线与相邻 Net 之最小距离在何处,本命令让使用者选到 Net 名称后,报告此 Net 所有连接物件 (包括 Pin、Via、Cline、Shape) 与其他邻近 Net 物件之最小距离。

3. Check Acute Angle

检查 Board file 上的各 Etch 层走线 (包含 Shape),将形成锐角者报告出来。

4. Silkscreen Audit

针对用户指定的 silkscreen 底片层上层面的 text、refdes、line 以及 shape 物件做各种检查,包括与 soldermask 间距,文字线宽、文字角度、Reference 位置错置等等。

5. Testprep Audit

让用户检查板子上测试点的距离以及测点 padstack 是否有作防焊开窗 (soldermask)。

6. Create VIP / VOP Mark

生成 VIP (Via In Pad) 以及 VOP (Via On Pad) 记号于指定的层面

7. Gerber Out Check

提供在 Layout 作业完毕后,准备输出 Gerber 数据前的检查作业。

确认整份数据的 DB 是否有问题,档案上是否存在未完成或未连接定义的数据…,及整体最后的 DRC update 作业,最后再通过 DRC Walker 做最后的人工确认。本功能可以依据需求来勾选所要执行的项目,并批次执行。

8. Pin Count

Board file 上面所使用的 Pin 脚种类统计,系统提供 SMD Pin及Through Pin 这两类零件 Pin 脚的统计数字,并可依脚数计算 layout 设计费用。

9. Reference Summary

让用户针对 Board File 的所有零件之 Reference 做一个总结报告。方便硬件工程师或组装生产线人员参考使用。

10. Graser GTD

依据所设定底片数据产生提供给 GerbTool 使用的快速索引链接档案。

在使用 GerbTool 加载 Gerber 数据进行检查时,仅需要加载该连结档案,GerbTool 就会依据 Board 的迭层顺序将 Gerber 数据自动加载,并自动设定各层面的属性。

High Speed Option

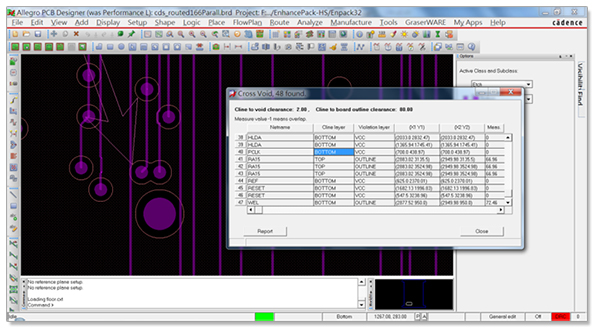

1. High Speed – Cross Void

在检查用户所选取的 Net 走线是否与 Void 或 Borad Outline 板框相距太近。

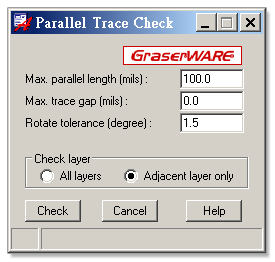

2. High Speed – Parallel Check

在检查用户所选取的高速 Net 走线在其他层相同位置之所有走线是否与其平行,其长度若超过指定长度,即算违规。

检查完成,若有违规,点击其中一项,画面会自动平移到坐标位置。

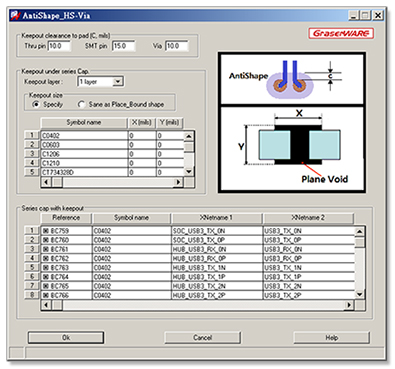

3. High Speed – Via AntiShape

检查用户所选取的 Differential Pair net (包含对应的 XNET) 走线于各个 Via 配对位置生成长圆形铜箔避开区,以及在 XNet 串接之电容底下也作出铜箔避开区。

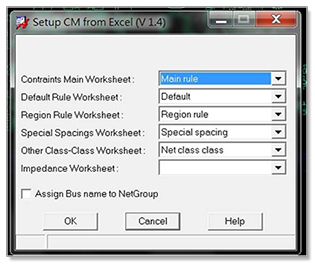

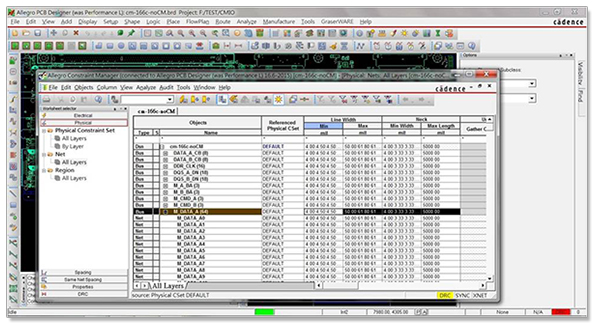

4. High Speed – CM Import

让用户可以在 Excel 定义 Constraint 再利用 CM Import 将定义载到 BRD 中。

可由 CM prepare 将 BRD 上的相关信号等定义萃取到 EXCEL 档案中。 |

|

可设定编辑 EXCEL 档案来定义 Constraint , 定义时不会占用 Allegro License。 |

|

编辑好的 EXCEL 档案可经由 CM Import 更新至 BRD 中。 |

PackagePack

对 APD / SiP 封装设计的辅助工具

1. Check Acute Angle

检查 Board file 上的各 Etch 层走线 (包含 Shape),将形成锐角者报告出来。

2. Mesh Shape Check

检查网状铜之线宽粗细 / 网目大小 / 角度是否为 90 度

3. Gold Plating

依照用户所选 mask 防焊层面,对该 mask 范围中 Top 或 Bottom 金属层所露出的 Pin、Via、Etch 物件自动生成所需镀金的 shape 范围图形。

4. Pin / Pin Length Report

本程序报告用户所选 Net 所有接线的顺序数据以及每对 Pin Pair 接线长度。

5. Copy Padstacks Pad

使用者可以很快地复制 Padstack 的某层 pad 图形或者钻孔图形。

6. Replace Padstack

替换焊盘或过孔,让可用框选和多选各焊盘或过孔之后以新 Padstack 替换。

7. Void Distance Check

让用户针对板子上各个 ETCH 层面 shape 物件内的 Void 之间的最小间距做检查与报告,并且检查两 shape 间距。