By Paul McLellan, Cadence

TSMC 高性能計算 (HPC) (也包括行動) 業務發展總監 Yujun Li 就「Advanced Technology for Smartphone and HPC Platforms (面向智慧手機和 HPC 平臺的先進技術) 」發表了演講。其中包括最先進的 N3 (3nm) 節點,這可能是推動 EDA 和先進 IP 發展最重要的技術。本文將介紹一下該演講的內容。

Yujun 首先介紹了半導體產業的驅動因素,現在超過一半的 IT 支出都用於雲資料中心。預計到今年年底,半導體行業將達到 5000 億美元的規模。這些龐大的數字反映了智慧城市、5G 以及 AI 賦能的發展。本文讓我們把目光轉向小數字。下面是 TSMC 的先進節點工藝路線圖,圖上的年份對應的是引入量產的時間。

該路線圖分為兩部分,頂部代表了高端性能,底部則是現在 TSMC 的主流技術,其工藝和庫在功耗和面積方面更加出色。

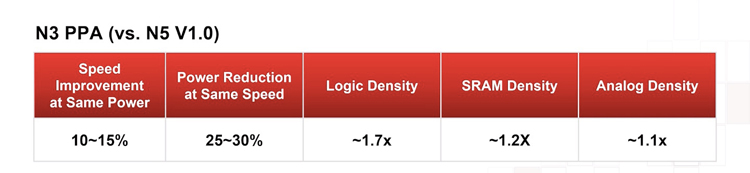

最新推出的技術是 N3,計畫在明年進行量產。從上表可以看出,與 N5 相比,N3的速度快了 10-15%,功耗低了 25-30%;邏輯密度提高了約 1.7 倍,SRAM 提高了 1.2 倍,類比也有小幅度改善。

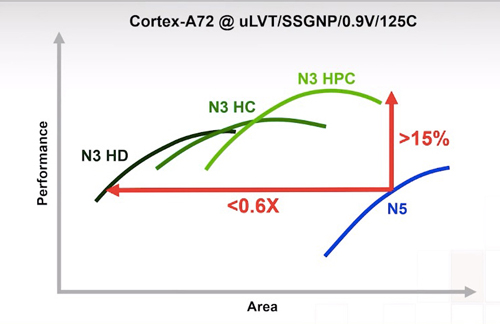

實際上,TSMC 有三種不同的 N3 庫:N3 HPC 庫的性能比 N5 提升了 15%;N3 HD 庫在相同的性能下,將設計的面積縮小了近一半; HC 庫則既能提高性能又能提高密度。

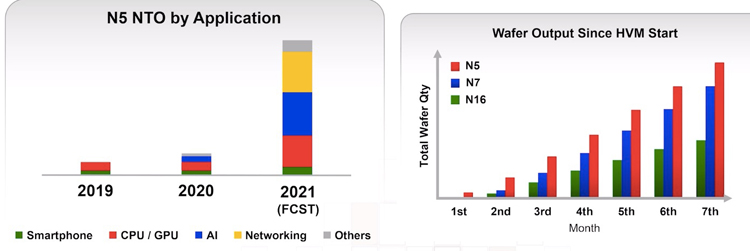

目前實現量產的最先進的工藝是 N5。最令人驚奇的事情之一是,產能爬坡從零開始。N5 的爬坡速度甚至比 N7 還快,比 N16 則快得多。在 HPC 和 5G 基礎設施的支持下,今年預計將有超過 40 個新的 N5 流片,流片產量也大幅增加。

接下來,Yujun 談到了去年推出的 N4。它是 N5 的光學縮小版,因此具有相同的設計規則。縮小後的晶片面積減少了 6%,而且也簡化了工藝並減少了掩膜的數量。在相同的產量下,功耗和性能比 N5 更為出色。N4 的試產於今年第三季度開始。

所有這些先進節點的一個重大挑戰是極紫外光罩 (EUV mask )缺陷和壽命。大家可能知道,這些光罩實際上是鏡子,而整個系統被封閉在深度真空中。缺陷已降至 2018 年的三分之一,光罩壽命卻增加了 4 倍,幾乎與傳統光刻技術相同。

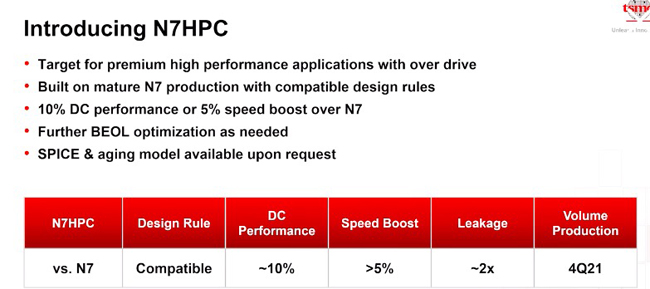

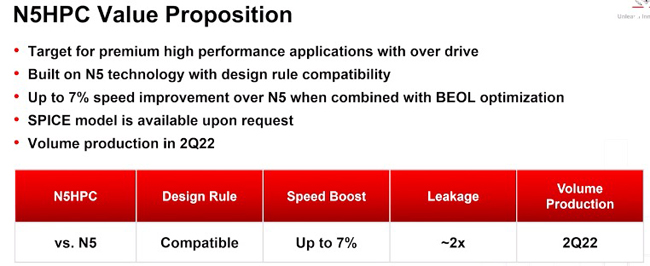

最後,TSMC 推出兩種新工藝:N7HPC 和支持超速的 N5HPC。這些工藝有更高的性能,但代價是漏電有所增加。這是自 28nm 以來,TSMC 第一次擁有針對 HPC 進行優化的工藝。資料詳見下面的表格:

綜上所述:

在 HPC、網路、高端智慧手機、人工智慧的推動下,大力遷移到先進制程 |

|

N7、N6、N5 投入大批量生產 |

|

N4 在 2021 年第三季度進行試產 |

|

N3 有望在 2022 年投產 |

|

同時推出 N7HPC (2021 年第四季度) 和 N5HPC (2022 年第二季度) |

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」